# FAIRLIGHT

# CMI SYSTEM SERVICE MANUAL

Scanned by J-B. Emond www.fairlight.free.fr

# CMI SYSTEM SERVICE MANUAL

..

and a second the subpression of the second second

# FAIRLIGHT INSTRUMENTS, JUNE 1982

•

## SECTION 1. INTRODUCTION TO C.M.I. MAINFRAME

#### 1.0 INTRODUCTION

The Fairlight Computer Musical Instrument is a complete music production and performance instrument. It is a special purpose computer system incorporating a custom dual M6800 central processor interfaced to special input-output devices optimised for the rather unusual requirements of music production.

The information presented in this manual is intended as a guide to give the reader an appreciation of the general operating principles of the C.M.I. In the event of a malfunction, it should be used to isolate which of the four main C.M.I. sub-systems is at fault, then for detailed functional information refer to the service manual for the item concerned.

Related documents are: C.M.I. MAINFRAME SERVICE MANUAL GRAPHICS TERMINAL SERVICE MANUAL ALPHA-NUMERIC KEYBOARD SERVICE MANUAL MUSIC KEYBOARD SERVICE MANUAL FLOPPY-DISK DRIVE SERVICE MANUAL

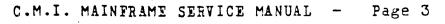

1.1 SYSTEM OVERVIEW

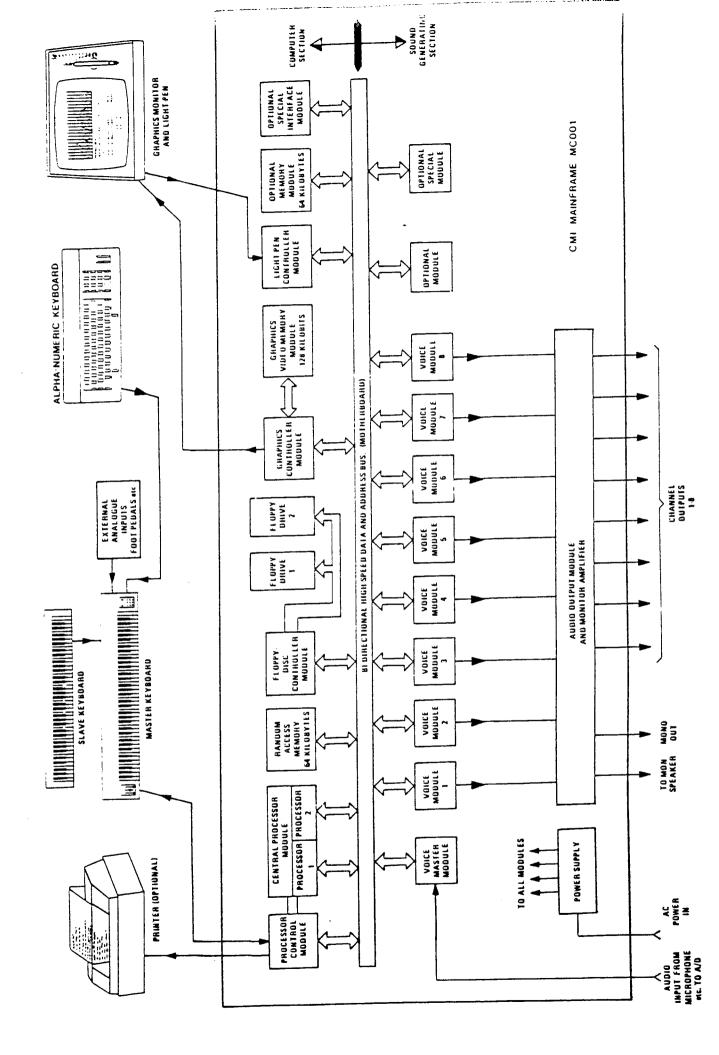

The system comprises for main units (Refer Fig. 1).

- 1) Mainframe: Houses the computer section, floppy disk drives, audio generation section and power supplies.

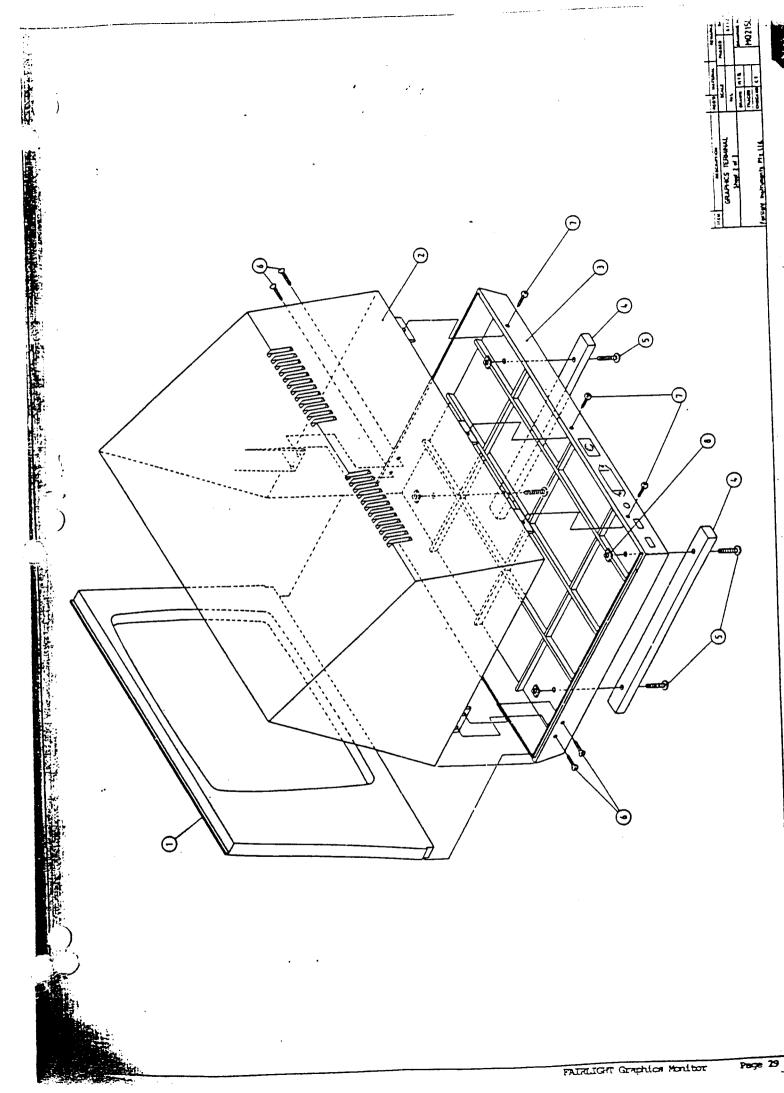

- 2) Graphics Terminal: The primary display terminal for the computer. It is a 15 inch C.R.T. display with lightpen.

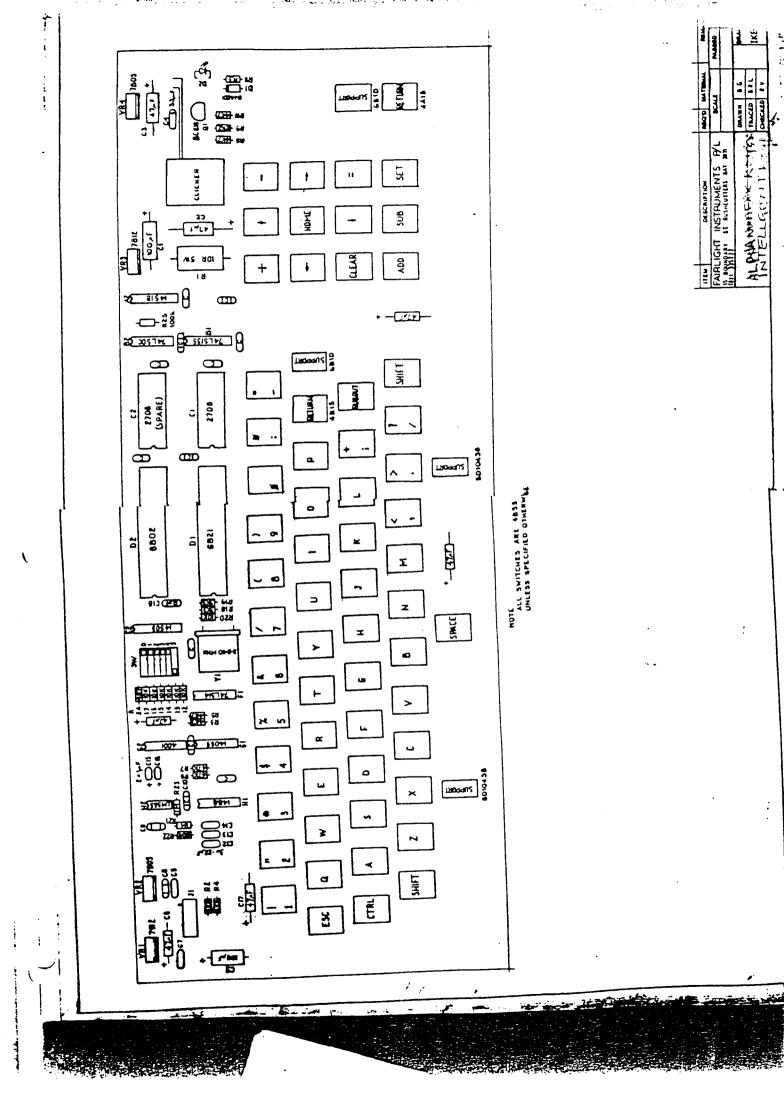

- Alphanumeric Keyboard: Sends serial ASCII data to the computer. Used for operator input of commands etc.

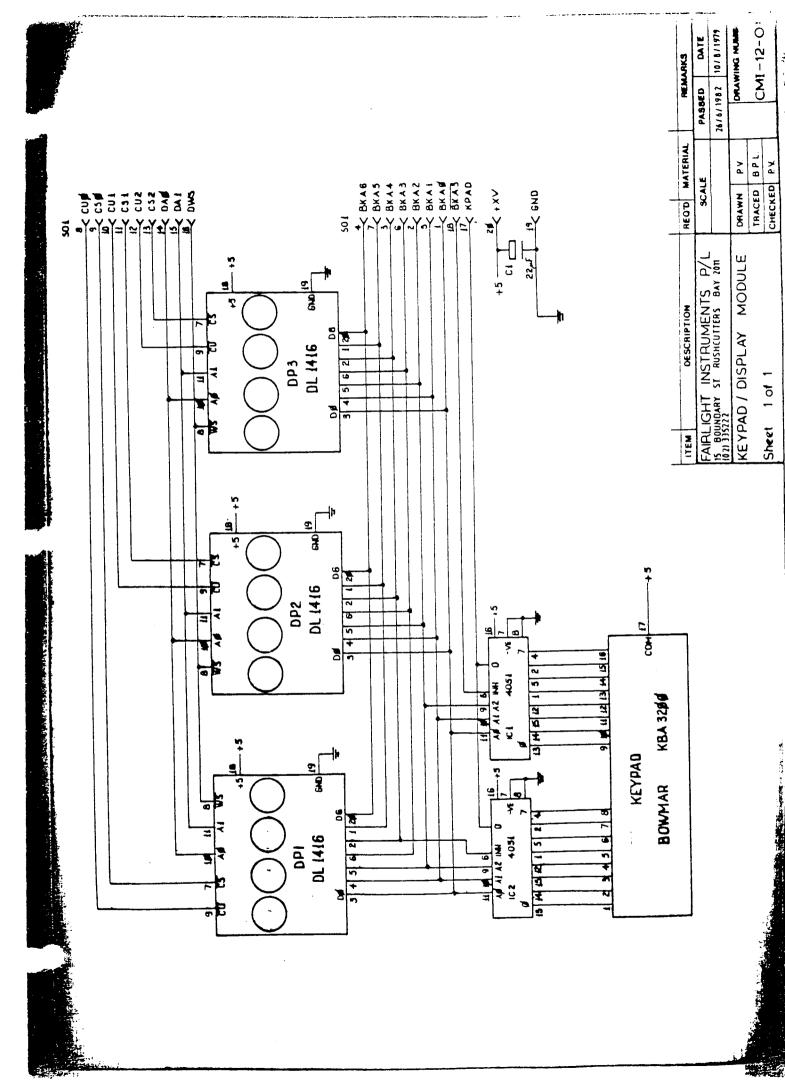

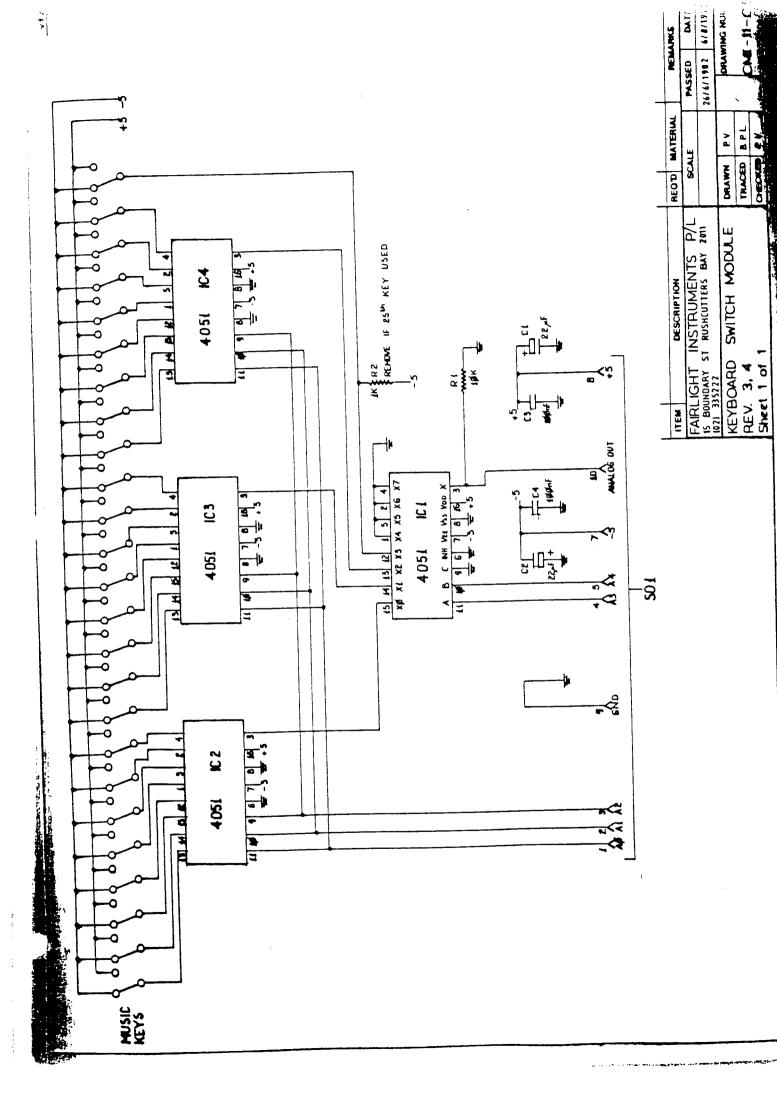

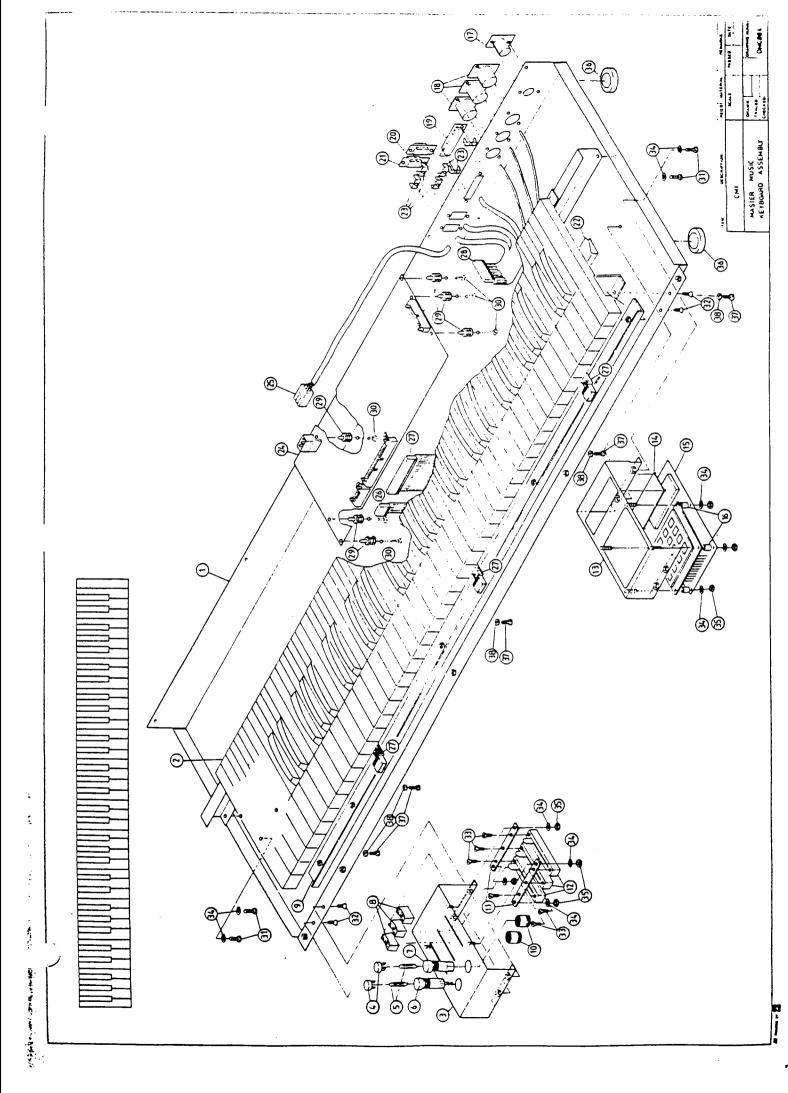

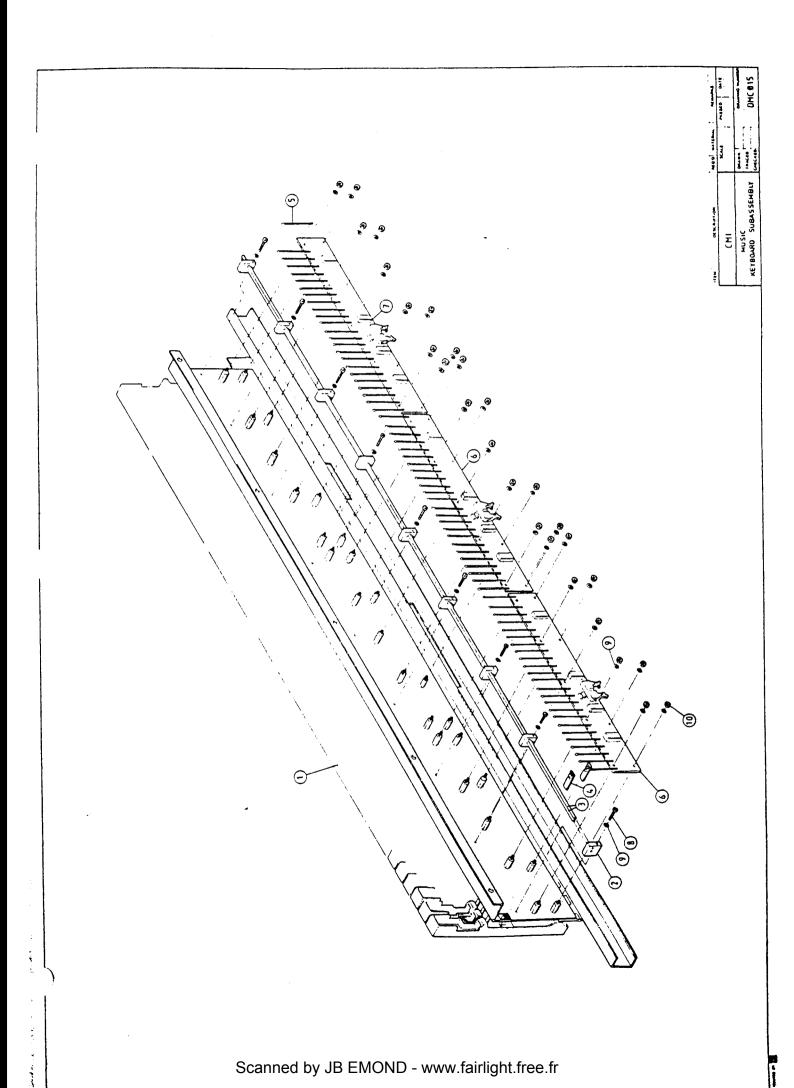

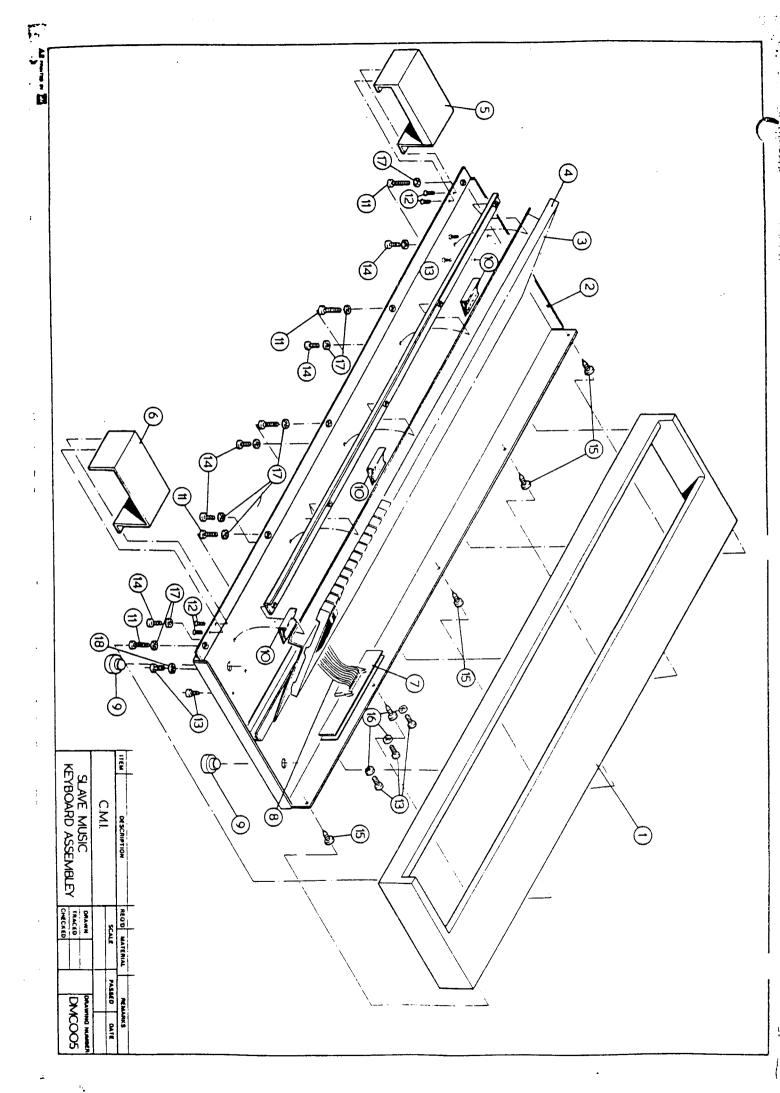

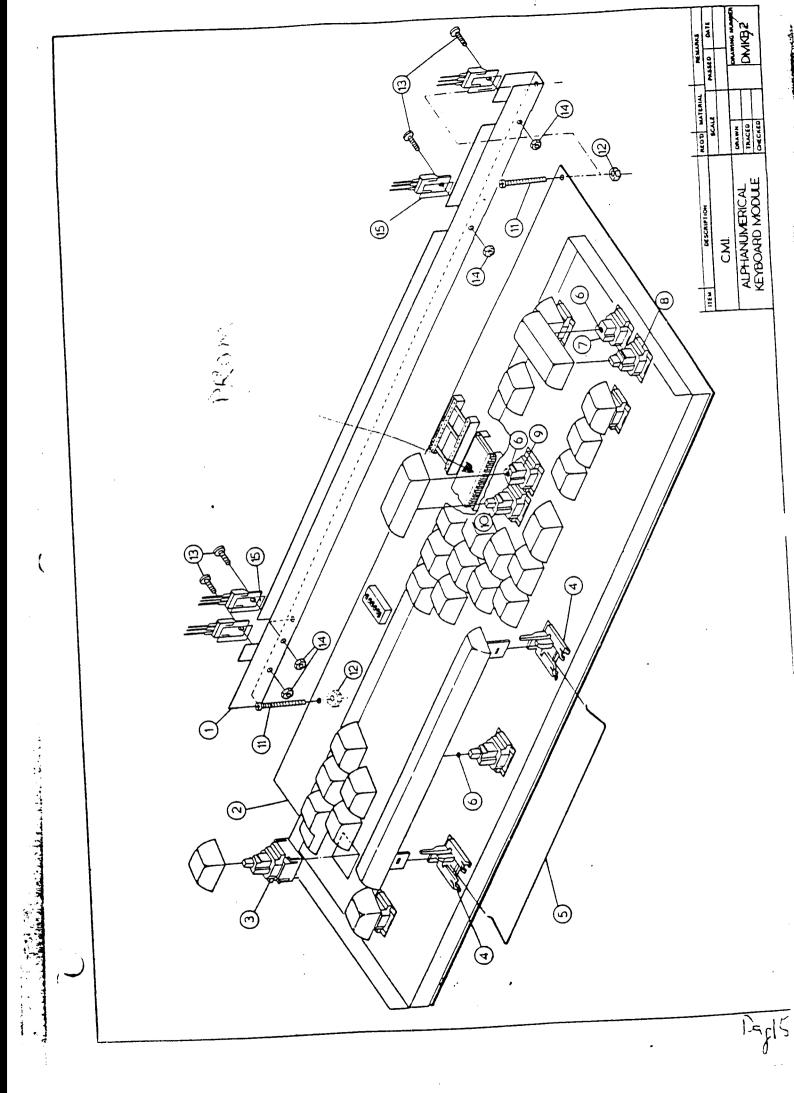

- 4) Music Keyboard: Piano-like keyboard sends serial data to the computer on each key depression. Used for live playing. Also includes several analog controls and switches which are digitised, and a numeric keypad with 12 character alpha-numeric display which serves as a secondary Input-Output device.

CMI SYSTEM SERVICE MANUAL

PAGE 2

, interest

States and second states

and the second sec

## SECTION 2. FUNCTIONAL DESCRIPTION

#### 2.1 C.M.I. MAINFRAME

The Mainframe houses the computer section of the C.M.I., that is all the digital control and sound generating hardware. It can be considered a stand-alone operational unit. With nothing connected to it it is possible to start up the system and bootstrap load the disks (BOOT the system). On power-up, EPROMS located on the C.P.U. Control Card Q-032 will control the Boot process.

As soon as a disk is placed in the left-hand drive (Drive O) a special sector known as the Boot Block is read into RAM and executed. The code in the Boot Block then completes the Boot by reading in the C.M.I. Operating System. The system is then ready to accept commands from the alpha-keyboard, music keyboard or light pen.

For deatailed information refer to the C.M.I. MAINFRAME SERVICE MANUAL.

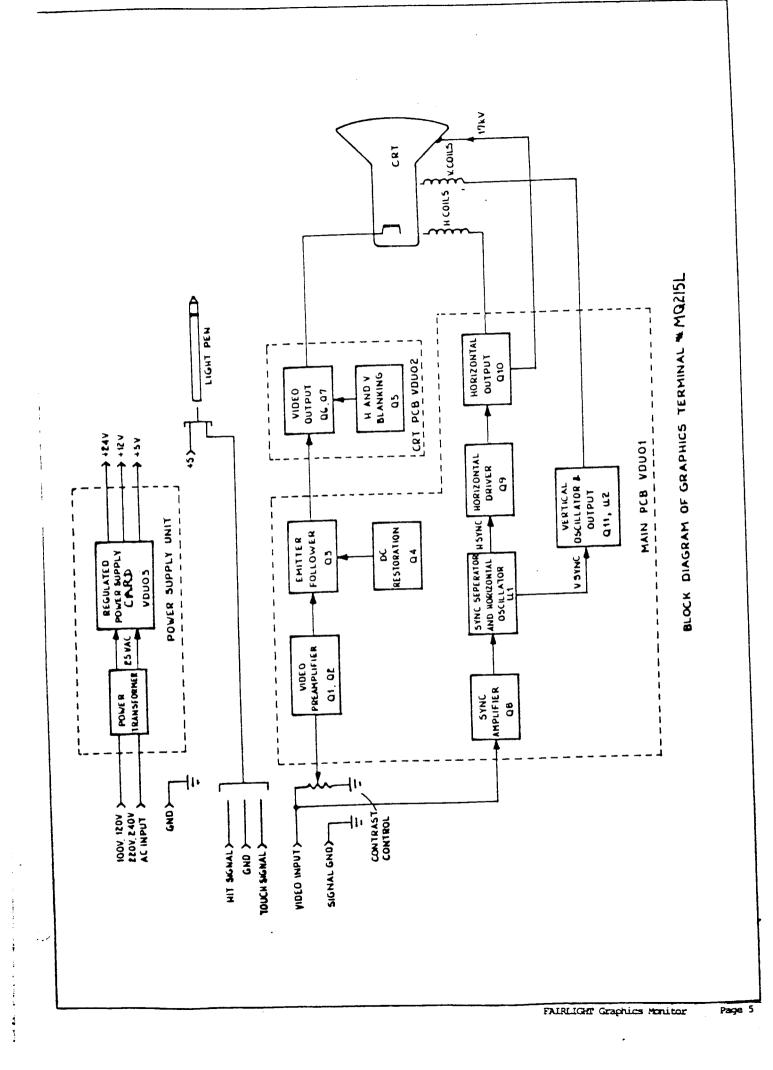

#### 2.2 GRAPHICS TERMINAL

•

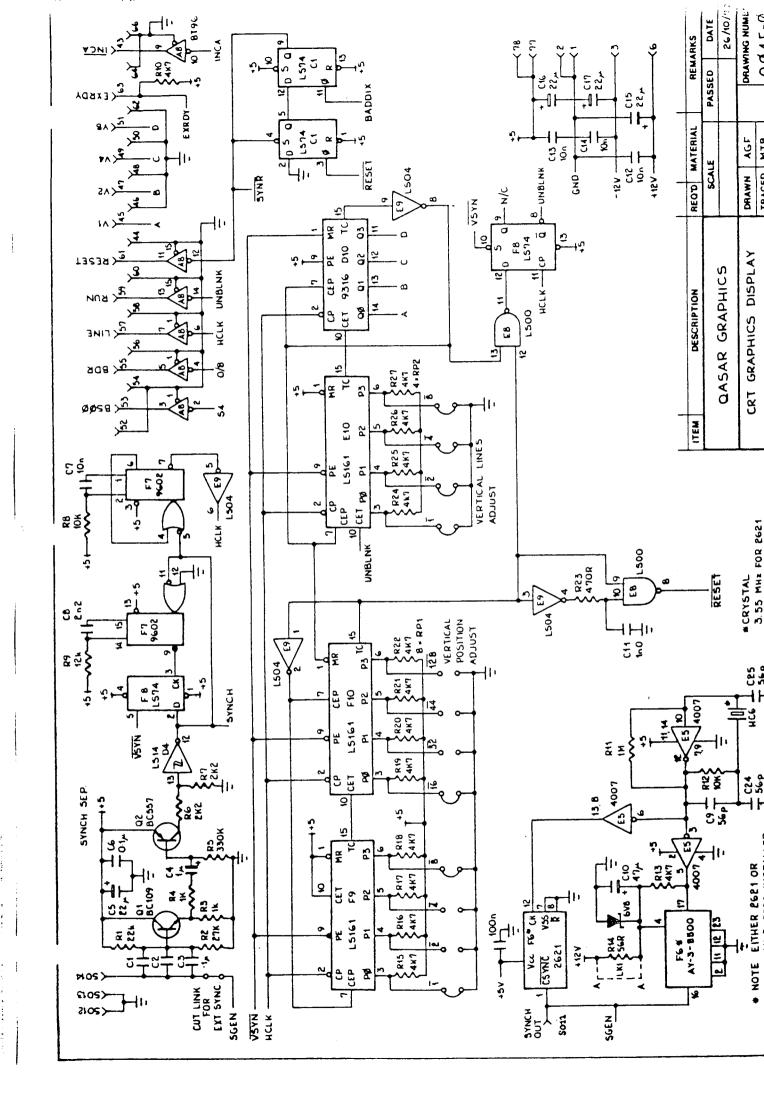

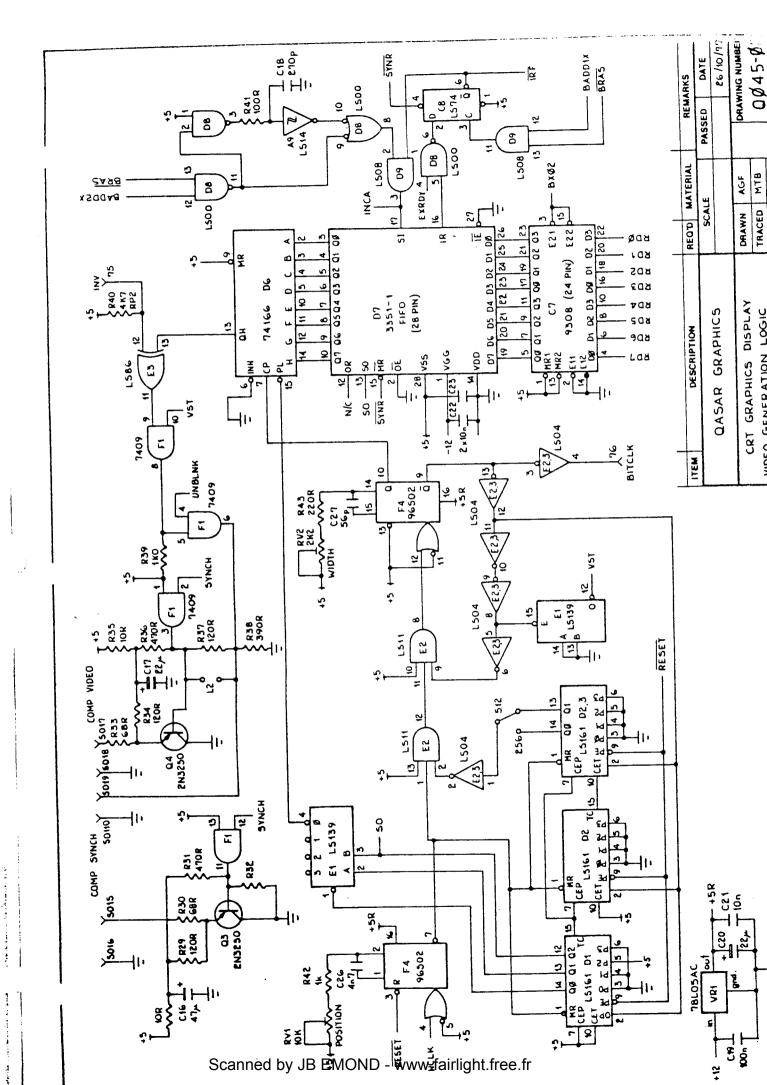

Display data for the Graphics Terminal is generated by the Graphics Display card Q-045 in the form of a composite video signal. The display format is a bit-mapped image of 16 kilobytes of VRAM, displayed as a 512 (Horizontal) by 256 (Vertical) matrix.

The Light-Pen operates by sending a pulse back to the computer when the phosphor dot is "seen" to flash past. The Light Pen Interface Q-14d, located in the Mainframe generates X-Y co-ordinates from the timing of this pulse. As well as this "Hit" signal from the lightpen, there is a "Touch" signal, which indicates that the operator has activated the pen by touching the end.

For detailed information, refer to the GRAPHICS TERMINAL SERVICE MANUAL.

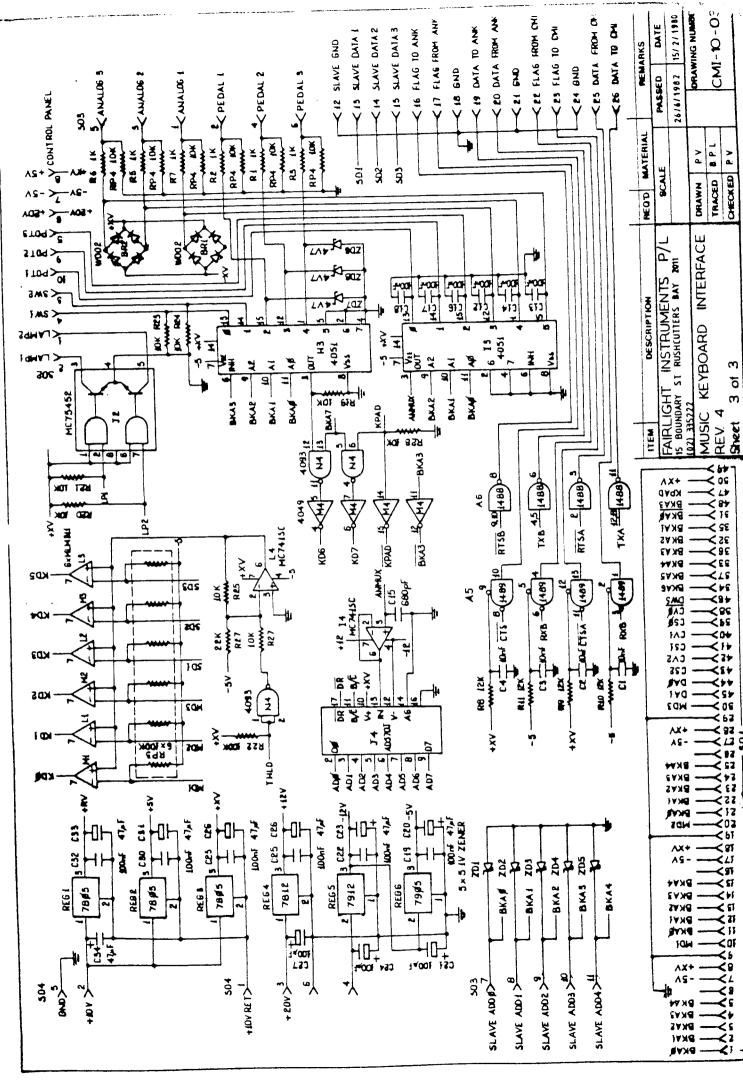

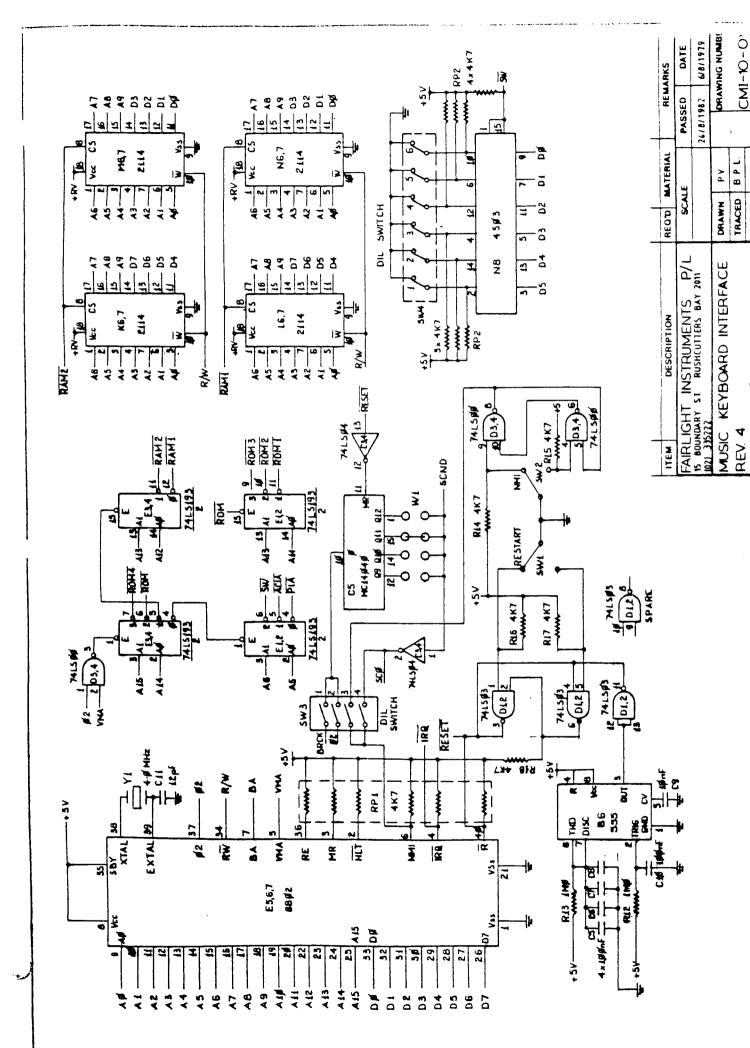

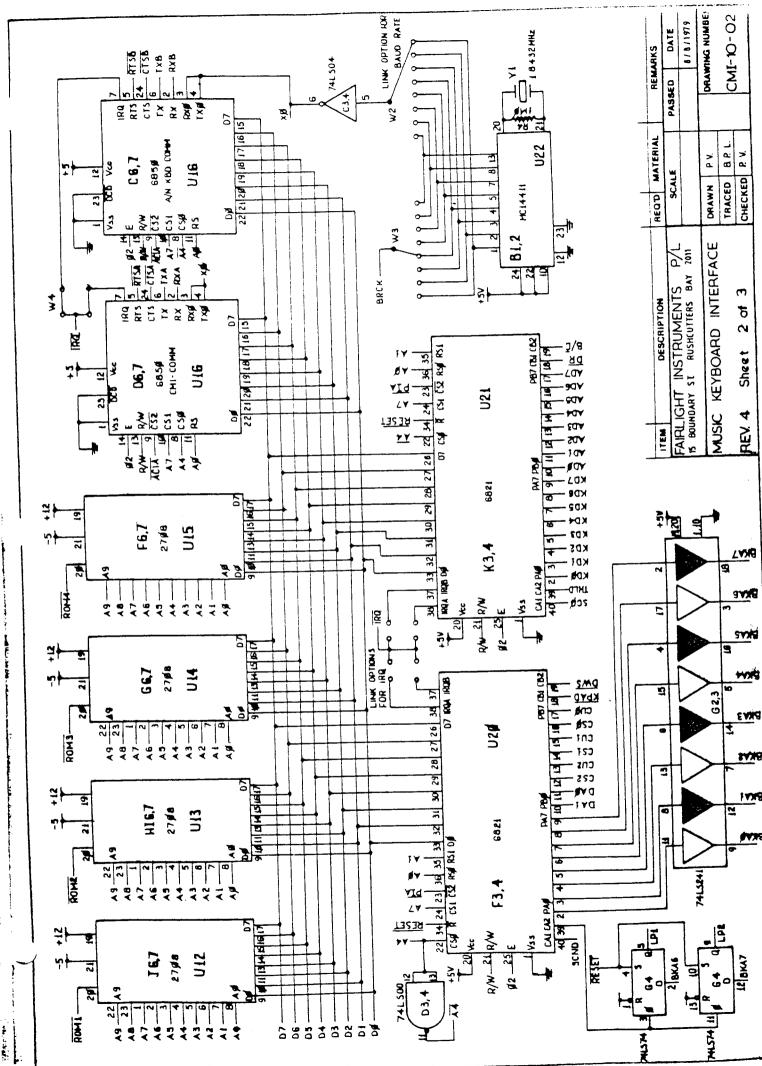

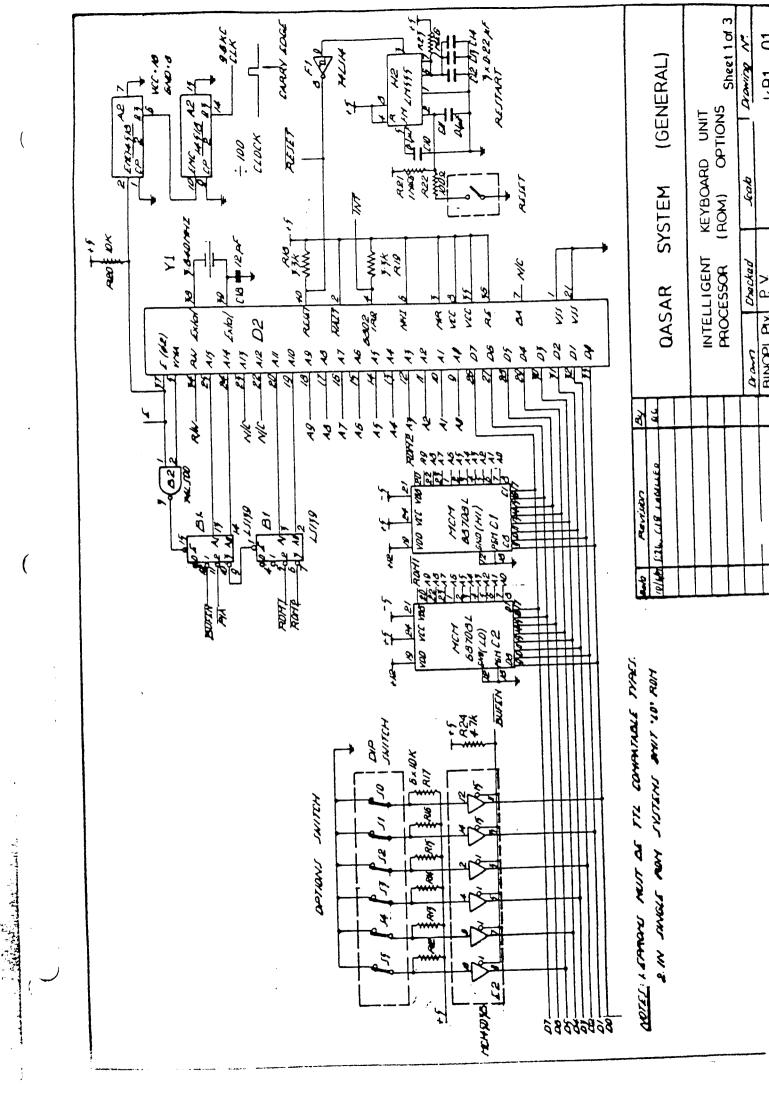

#### 2.3 MUSIC KEYBOARD

The music keyboard interfaces to the Mainframe via a bi-directional RS-232C port located on the processor control card Q-032. The Baud rate is selected by the Terminal Speed control on the from panel of the mainframe, and D.I.L. switches inside the keyboard. Both of these must be set to 9600 Baud.

The keyboard is controlled by an on-card M6802 microprocessor executing a program in EPROM. As well as data communications with the Mainframe, data coming in from the alpha-numeric keyboard is preprocessed before being forwarded to the mainframe.

CMI SYSTEM SERVICE MANUAL

PAGE 4

Data is sent to the computer whenever:

- 1) A music key is depressed or released

- 3) A key on the alpha keyboard is pressed

- 3) One of the three faders is moved

- 4) A switch or pedal plugged into the keyboard is operated

Keystroke data is sent in the form of three-byte packets. This includes keyboard number, key number, depression/release flag and key velocity data. Key velocity is calculated by the on-card processor which times the flight of the key contact as it travels between two ousbars.

The 12 digit alpha-numeric display on the right-hand end of the keyboard is used to display messages to the operator in circumstances where the Graphics Terminal is not being used. The display is controlled by the processor on the keyboard. On power-up, the message - POWER ON - is displayed. This is generated locally by the keyboard itself. Once Booting has commenced, the message LOADING is dispalyed. This message is sent by the mainframe, via the serial link.

The control devices (faders, switches and pedals) are digitised by an eight-bit Analogue to Digital converter in the music keyboard and when the data changes, a packet of data is transmitted down the serial link to the mainframe.

For detailed information, refer to the MUSIC KEYBOARD SERVICE MANUAL.

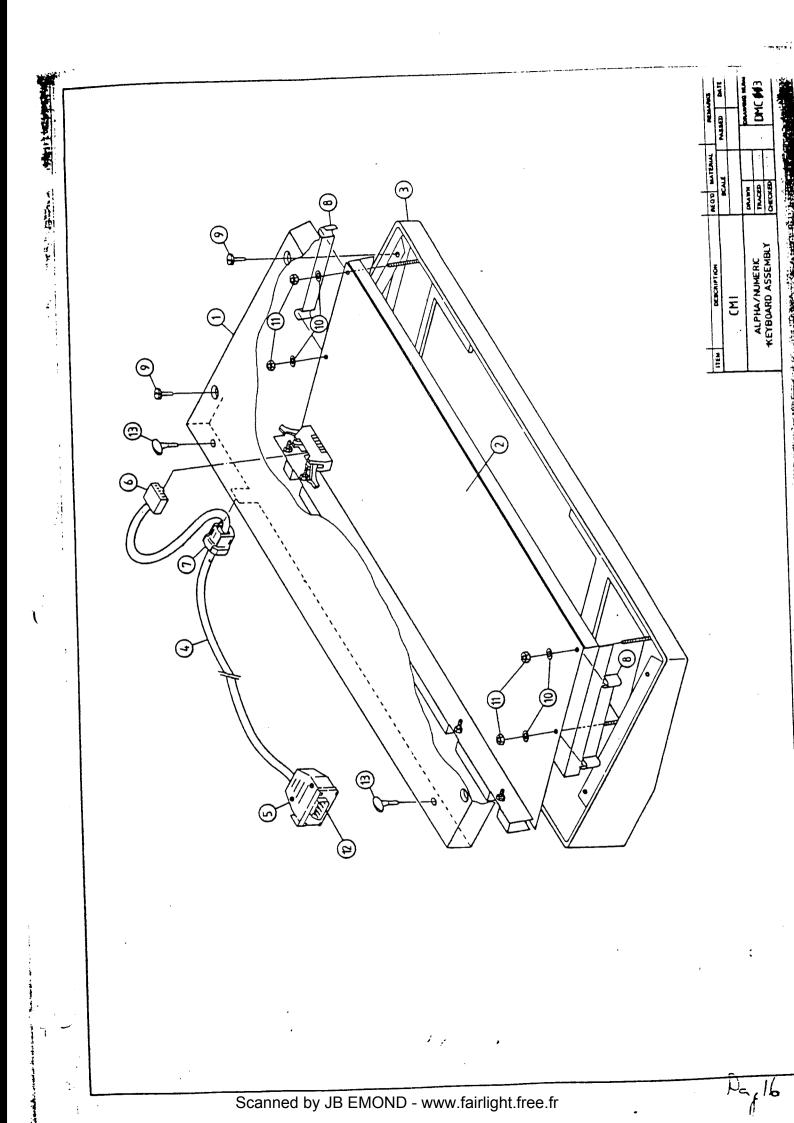

#### 2.4 ALPHA-NUMERIC KEYBOARD

This keyboard uses another M6802 microprocessor which controls scanning of the o2 Hall-effect switches and serialises the data which is transmitted in ASCII format, RS-232C protocol. Data rate used is 9600 Baud, selected by D.I.L. switches on the circuit board. The processor executes firmware stored in EPROM.

Normally the alpha-numeric keyboard is plugged into the music keyboard. It receives its power from there, and sends its data to the processor in the music keyboard. The data is flagged as alpha-numeric, queued until there is no music keyboard data, and then forwarded to the mainframe. If desired, the alpha keyboard can be plugged directly into the Keyboard connector on the mainframe, bypassing the music keyboard. This can be a useful diagnostic aid.

#### 2.5 INTERCONNECTING CABLES

1

The four major sub-systems are connected by pluggable cable sets which should be treated with the same suspicion warranted by mechanical parts. The signals carried by each cable, together with pin numbers, are described fully in section 4, below.

#### SECTION 3. TROUBLESHOOTING

111

This section covers troubleshooting the C.M.I. system only to the level of identifying which of the four sub-systems (mainframe, music keyboard, alpha-keyboard or graphics terminal) is at fault. Having done this, service personel should refer to the service manual for the offending item.

NOTE: Remember that the C.M.I. is a complex piece of hardware running sophisticated software, and it is sometimes hard to differentiate between a hardware fault, software bug, and operator error. If there is any douot, the same sequence of operations should be tried on a known good system before attempting hardware repairs. In executing the following diagnostic procedures, the serviceman should be aware that a faulty System Disk can cause what appears to be hardware faults. Furthermore, hardware faults can cause disks to be destroyed, either physically or by corrupting data, so it is wise to keep a good supply of C.M.I. system disks and diagnostic disks on hand.

3.1 FAULT ISOLATION BY SUB-SYSTEM SUBSTITUTION

The easiset way to identify the faulty sub-system is to exchange whole units for known good ones if such are available. If a complete working system is on nand, exchange each sub-system in turn, starting with the most likely to be responsible for a given fault. Some common fault symptoms and suggested substitution procedures follow.

3.1.1 System will not boot. (Sucessful Boot is indicated by Page 1 appearing on the screen, or Page 1 Ready message at the music keyboard).

Unplug keyboard from mainframe. If it still does not boot, the fault is in the mainframe. If it does boot, try substituting the music keyboard. If it still does not boot, substitute the alpha-keyboard. The Graphics Terminal should not be able to affect booting. If the problem does not go away at any stage, substitute the interconnecting cables one by one.

3.1.2 System boots (Page 1 on screen or message at keyboard) but does not respond to alpha keyboard commands.

Substitute music keyboard, then alpha keyboard, then graphics terminal, then cables. If problem persists, the fault is in the mainframe.

3.1.3 No sound when voice loaded and music keyboard played.

Substitute music keyboard first, then cables, then alpha keybaord, then granics terminal. Plug the alpha-keyboard into the mainframe directly, and hit <CNTRL P>. A note should play. If not, the fault is in the mainframe.

3.1.4 System works properly except Graphics display or lightpen malfunctions.

Substitute graphics terminal and cable first. If no better, fault is almost certainly in mainframe.

3.1.5 Other strange behaviour.

**...**

ł

Start by substituting mainframe.

3.2 SUB-SYSTEM CHECKOUT WITHOUT SUBSTITUTION

In many cases the faulty sub-system will have to be identified using only commonly available test equipment. Minimum requirements are a multimeter for measuring volts D.C. and resistance, an oscilloscope, and the usual set of tools such as screw drivers, pliers, soldering iron etc.

The faulty suc-system can usually be isolated by the following tests:

3.2.1 System will not boot.

Unplug keyboard input and try again. If system does not boot, fault is in mainframe. If it now boots, fault is in music keyboard, alpha keyboard or cables. To isolate which, try again with alpha keyboard plugged straight into mainframe to eliminate music keyboard.

3.1.2 System boots but does not respond to alpha keyboard commands.

Most likely fault is in alpha-keyboard or cable. If the keyboard does not click when a key is pressed, either the keyboard is faulty or the power supply to the keyboard has failed. Check the supplies and data output at the keyboard plug using the Signal List (Section 4, below).

3.1.3 No sound when voice loaded and music keyboard played.

Check for normal operation with the alpha-keyboard plugged directly into the mainframe. A note should be heard if  $\langle CTRL P \rangle$  is pressed with a voice loaded. If this works, then the music keyboard or cable is probably faulty. Check for the correct signals at the power and signal connectors at the music keyboard. (Refer section 4).

If there is no sound in response to the <CNTRL P>, then the fault is in the mainframe.

PAGE 7

3.1.4 System works properly except Graphics Terminal malfunctions.

Check video ouput signal at the Graphics connector. If this is normal, fault is in Graphics Terminal or cable. Note that a negative image can be caused by a fault in the graphics terminal or the mainframe, and cannot be easily seen by looking at the signal on an oscilloscope. To achieve a substantially black image for examination with the oscilloscope, remove the system disk and restart both processors. This will result in just the words CMI READY on a black screen, in which case the scope display should show any fault clearly.

3.1.5 Lightpen does not work but everything else normal.

Point the lightpen at a light area of the screen. If there is a cursor which disappears when the Touch is activated, then the fault is in the mainframe. Otherwise the fault may be in the Graphics Terminal, lightpen or cables. Check for proper Hit and Touch signals at the Graphics connector at the mainframe by unplugging the cable and using an oscilloscope. If these are not correct the fault is in the Graphics Terminal. Otherwise the mainframe is faulty.

3.1.6 Other strange behaviour.

· •...

, T Most other faults such as improper operation of one or more of the sound channels or unreliable reponse from the computer can be attributed to a fault in the mainframe. To eliminate all other posibilities a useful diagnostic trick is to start the system playing a long M.C.L. or Page 9 Sequencer loop and un-plug all cables except the mains input and audio ouput. If the fault is still evident, then the mainframe is definitely to blame. 1

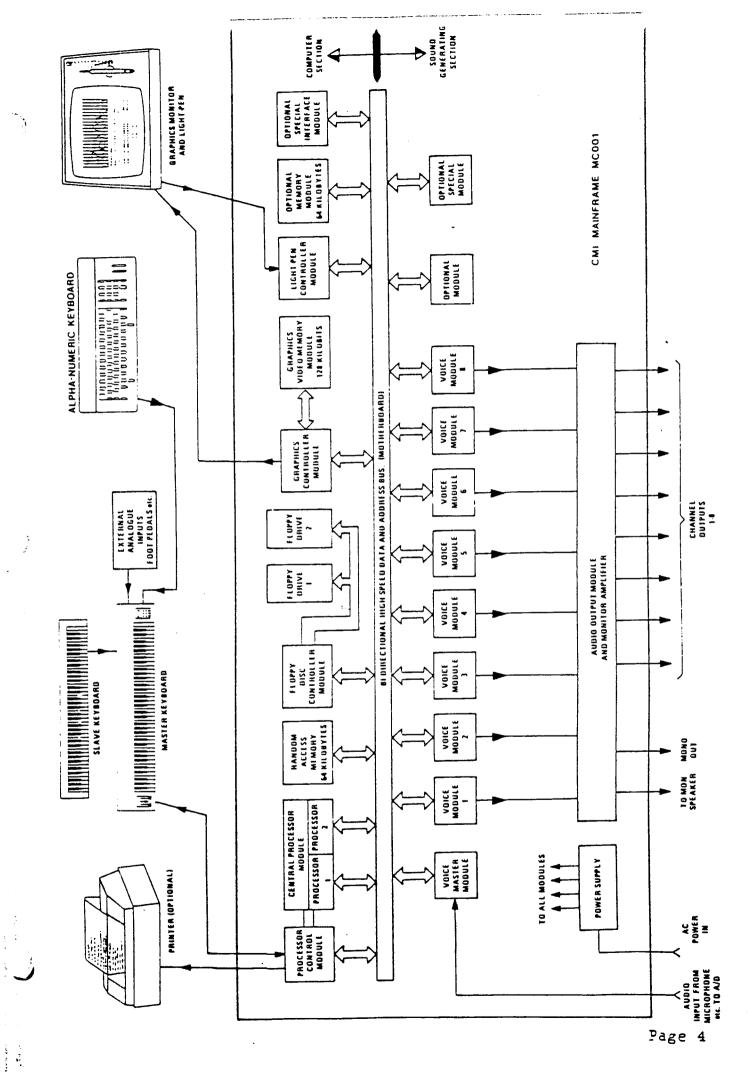

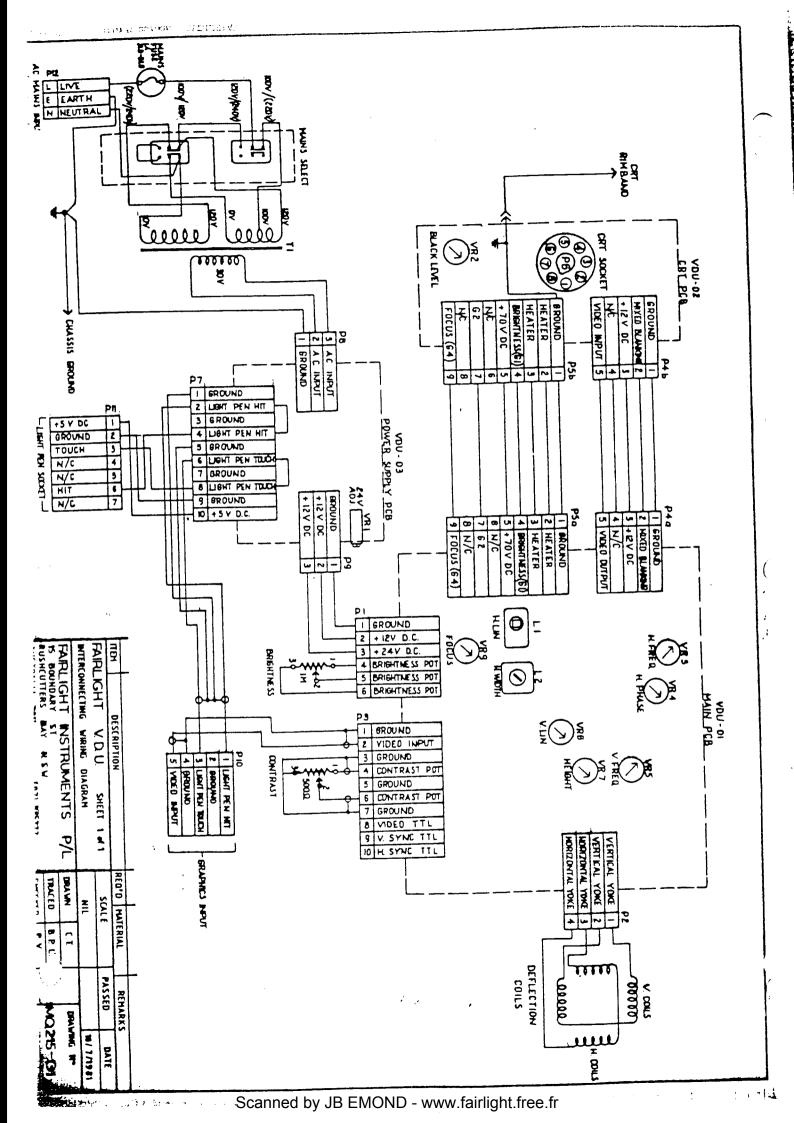

This section describes the signals present in each conductor of each interconnecting cable in the C.M.I. System when functioning normally. Refer to Figure 2 for cable identification.

4.1 Mains Cable: Part no. MC006 (Cannon) or MC068 (I.E.C.)

A.C. Mains Neutral, Active and Ground.

4.2 Graphics Terminal Power: MC007 (Cannon) or MC067 (I.E.C.)

A.C. Mains supply to Graphics Terminal. Switched by key switch on mainframe. This supply is always the same as the local mains potential.

3 blindii ser grine 4.3 Graphics Terminal Signal: MC065

Video signal to Graphics Terminal and Light Pen signals to mainframe.

Connector Type: Cannon 5-pin.

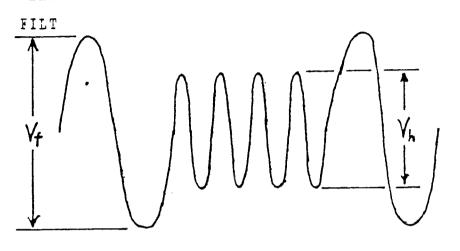

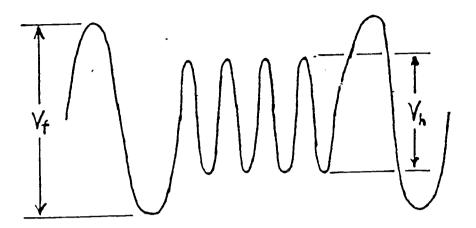

- Lightpen Hit. T.T.L. level, asserted low. On oscilloscope, appears as a series of low-going pulses Pin 1 about luS wide, repeated every 20mS, when the pen is pointed at a bright area of the screen. (See fig 3a)

Pin 4

Pin 5

Sundar Remel

(h) wester

- - -

with here it

and with the

Kase (Li

willie ??

aller a she wanted and

and the second se

- Lightpen Signal Return. Ground for lightpen signal Pin 2 cables.

- Lightpen Touch. T.T.L. level, asserted low. Normally at approx +4 volts, goes low (less than 0.4 V) when the Pin 3 end of the lightpen touched.

Video Return. Ground for Video signal cable.

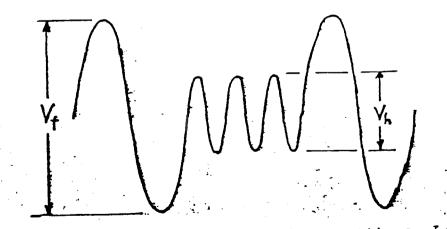

Composite Video. 1V P-P video signal to Groaphics display. Format is 625 lines, 50 Hz frame rate. (See fig 3b)

Figure 3 b COMPOSITE VIDEO

Figure 3a LIGHTPEN HIT SIGNAL

4.4 Music Keyboard Power: MC064

Unregulated power supply to music keyboard (also indiectly supplies alphanumeric keyboard).

Connector Type: Cannon 7-pin.

CMI SYSTEM SERVICE MANUAL

PAGE 10

Pins 1,2 +10V Return. Return (ground) for +10V supply.

Pins 3,4 +10V Supply. Unregulated supply, +9 to +11 volts.

- Pin 5 -20V Supply. Unregulated supply, -18 to -22 volts.

- Pin 6 +20,-20 Return. Return (ground) for + and 20 supplies.

- Pin 7 +20V Supply. Unregulated supply, +18 to +22 volts.

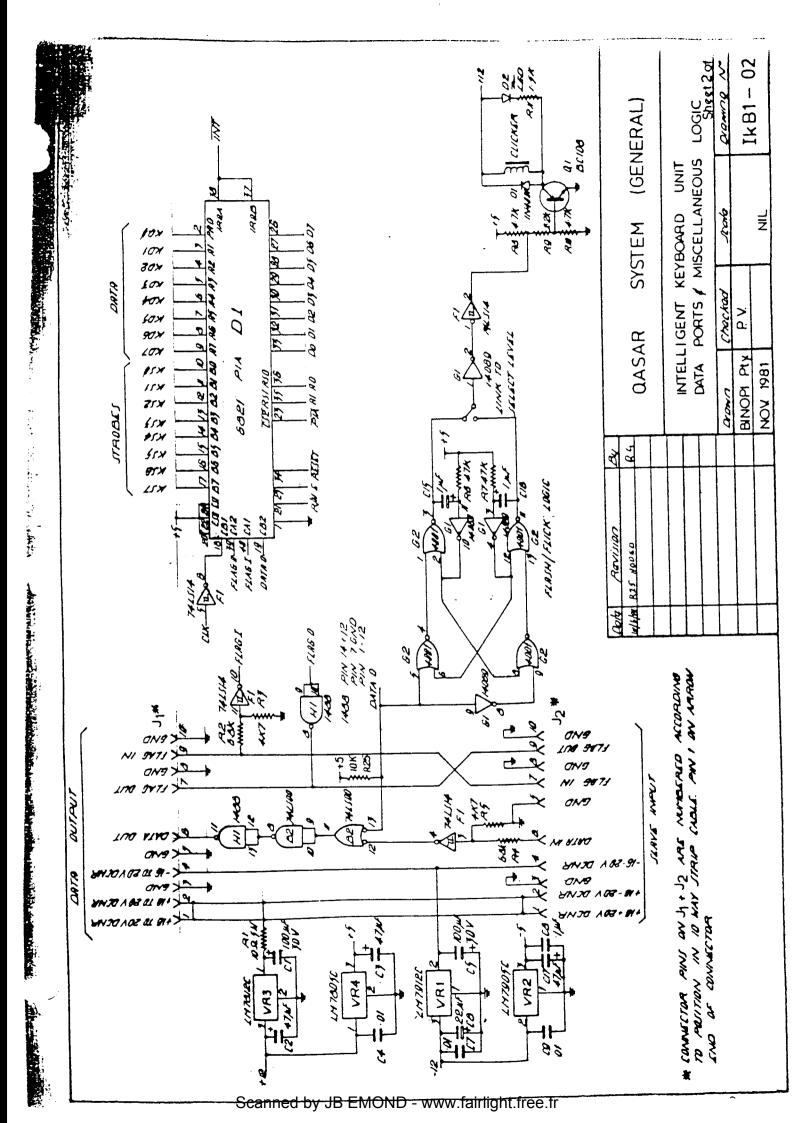

#### 4.5 Music Keyboard Signal: MC060

-----

Bi-directional serial data between mainframe and music keyboard, including "busy" flags in both directions. Power supply is also carried by this cable, to power the alpha-numeric keyboard if it is connected instead of the music keyboard.

Connector Type: 9 Pin "D-Mini"

- Pin 1 +18 to 22 volts unregulated supply. This is not used by the music keyboard.

- Pin 2 DON1. Signal to enable transmission of data from the keyboard. RS-232 levels. Enabled: >7 volts. Disabled <-7 volts. With nothing being transmitted from the keyboard, this signal should be at approx. +10 volts. When keys are pressed or released a burst of -10 volt pulses should be seen for between 2 and 10 milliseconds.

- Pin 3 -18 to -22 volts unregulated supply. This is not used by the music keyboard.

- Pin 4 FLAG1. Signal to diasble transmission of data from the mainframe to the keyboard. Signal is normally +10 volts.

- Pin 5 SIGNAL RETURN. Ground for data paths.

- Pin 6 DATA IN. Serial data from keyboard to mainframe. Format is RS-232. Normally at -10 volts. When a key is pressed or released a burst of +10 volt pulses lasting approx. 3 mS sholud be seen.

- Pin 7 POWER RETURN. Return (Ground) for + and supplies.

- Pin 8 Not Connected.

- Pin 9 DATA1. Serial data from mainframe to keyboard. Format is RS-232. Normally at -10 volts. For each character sent from the mainframe to the alpha-numeric display a burst of +10 volt pulses lasting approx. 1 mS should be seen.

4.6 Alpha-numeric Keyboard Power/Signal : MC013

Unregulated power supplies to alphanumeric keyboard, serial data from alphanumeric keyboard.

Connector Type: 9 Pin "D-Mini"

- Pin 1 +18 to 22 volts unregulated supply.

- Pin 2 Not Connected.

- Pin 3 -18 to -22 volts unregulated supply.

- Pin 4 Not Connected.

- Pin 5 SIGNAL RETURN. Ground for data paths.

- Pin 6 DATA OUT. Serial data from keyboard. Format is RS-232. Normally at -10 volts. Each time a key is pressed a burst of +10 volt pulses lasting approx. 1 mS should be seen.

- Pin 7 POWER RETURN. Return (Ground) for + and supplies.

- Pin 8 Not Connected.

- Pin 9 Not Connected.

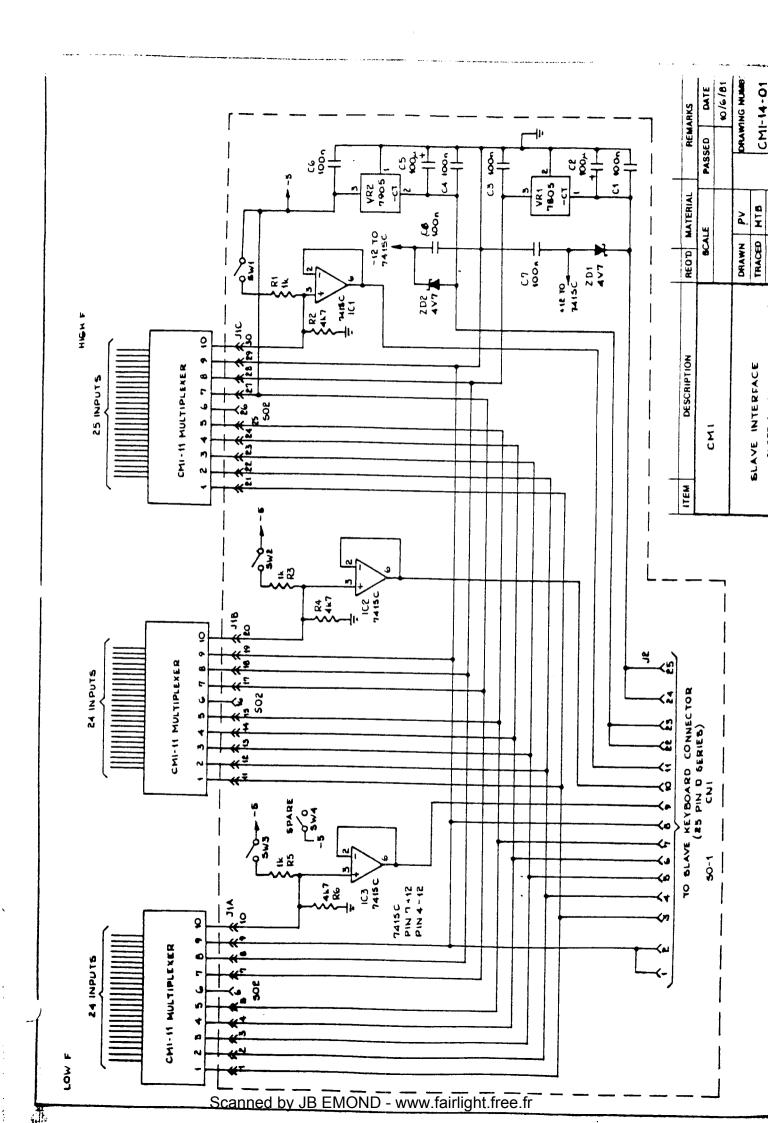

- 4.7 Slave Keyboard Power/Signal : MC059

The Music Keyboard sends power and key multiplexer addressing data to the slave keyboard. Key data is returned from the slave keyboard.

- Connector Type: "D Mini" 25-pin.

- Pins 1,2 POWER SUPPLY RETURN. Ground.

- Pin 3 KEY ADDRESS 0 Least significant key multiplexer address bit. CMOS logic levels.

- Pins 4,7 KEY ADDRESS BITS 1-4. CMOS Logic levels

- Pin 8 SIGNAL RETURN Ground.

- Pin 9 KEY DATA 1. Data returned from key multiplexer scanning the lowest 24 keys. Normally at approx. -5 volts. Goes to 0 volts while key is in flight, and +5 volts when key is at rest in fully depressed position.

- Pin 10 KEY DATA 2. Data from middle 24 keys.

- Pin 11 KEY DATA 3. Data from top 25 keys.

CMI SYSTEM SERVICE MANUAL Scanned by JB EMOND - www.fairlight.free.fr Pins 11-21 Not Connected

- Pins 22,23 -20 SUPPLY. Unregulated power supply to slave keyboard, +18 to +22 volts.

- Pins 24,25 +20 SUPPLY. Unregulated power supply to slave keyboard, -18 to +22 volts.

4.8 Printer : MC062 9600 KAUD

Serial data from mainframe to printer, "busy" flag from printer to mainframe, plus "device on" signal used to switch on printer in readiness to receive data.

Connector type: Cannon 5 pin.

- Pin 1 Signal Ground.

- Pin 2 Not Connected.

- Pin 3 FLAGO. "Busy" flag from printer. RS-232 levels. <-7 volts when printer ready, >+7 volts when printer busy.

- Pin 4 DONO. "Device On" control from mainframe to printer. RS-232 level, >+7 volts to enable printer, <-7 volts to diable printer. This signal is optional as some printers do not require it.

- Pin 5 DATAO. Serial data to printer. RS-232 levels, ASCII format. Normally at -10 volts. For each character sent from the mainframe to the printer a burst of +10 volt pulses lasting approx. 1 mS should be seen.

4.9 Phones

Output for driving headphones. Monitors the MIXED LINE output. Internally, this output is taken from the MONITOR (speaker) output via a 100 ohm resistor.

Connector type: 1/4" (6.25 MM) stereo phono jack.

The following signal lists refer to connectors on the rear of the C.M.I. Mainframe.

4.10 Monitor

Output for driving a monitor speaker. The internal monitor amplifier will deliver a maximum of 20 watts R.M.S. into an 8 ohm speaker. Note that the Mainframe is fitted with a 1 amp speaker fuse which will blow if the monitor amplifier is driven to full output under load for more than a second.

Connector Type: Cannon 3 pin.

Pins 1,2 Ground

Pin 3 Active. With all channels producing a full-amplitude sinewave and the MONITOR control turned up to the point of clipping, this output should be approx. 38 volts P-P (with no load)

4.11 Channels 1-3

1.2.

Individual channel outputs (balanced, 600 ohms impedance).

Connector type: Cannon 3 pin.

- Pin 1 Ground

- Pin 2 Output Cold. Anti-phase output, maximum level 3.7 volts P-P.

- Pin 3 Output Hot. Maximum level 3.7 volts P-P.

4.12 Mixed Line Output

Mixed output of all eight channels (balanced, 600 ohms impedance).

Connector Type: Cannon 3-Pin

Pin 1 Ground

- Pin 2 Output Cold. Anti-phase output, maximum level 3.7 volts P-P.

- Pin 3 Output Hot. Maximum level 3.7 volts P-P.

#### 4.13 Sync

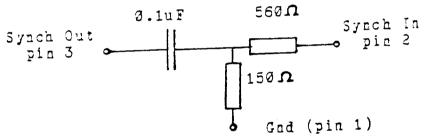

Synchronising input and output, for use with Music Composition Language (Page C) or Keyboard Sequencer (Page 9). This connector serves as both an input and ouput.

Connector type: Cannon 3-pin.

- Pin 1 GROUND

- Pin 2 Sync Input. Pulses or tone of 1 to 20 volts P-P. Waveform unimportant. Frequency range 2 Hz to 5 kHz. Impedance 10 K ohms.

- Pin 3 Click Output. Periodic pulse, rate controlled by Page 9 Sequencer or M.C.L. (Page C). Waveform is a spike of approx. 5 volts peak, approx. 5 mS wide, alternately positive and negative going.

#### 4.14 Filter Output

Output of the bandpass filter used by the Analogue to Digital converter. It is designed to enable the operator to monitor the effect of various bandpass filter settings.

Connector type: Cannon 3-pin.

- Pin 1 GROUND

- Pin 2 GROUND

- Pin 3 OUTPUT. Amplitude for full-scale conversion is 10 volts P-P. Source impedance 600 ohms.

#### 4.15 Mic In

4

1

Balanced, 600 ohms input suitable for high output dynamic or condenser microphones. When the MIC/LINE switch is in the MIC position, this input is fed to the Analogue to Digital converter.

Connector Type: Cannon 3-pin

• .

Pin 1 GROUND

Pin 2 INPUT A

Pin 3 INPUT B

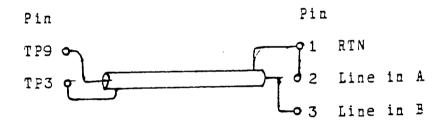

4.16 Line In

Balanced, 600 ohm line level input. This input is connected to the Analogue to Digital converter when the MIC/LINE switch is in the LINE position.

Connector Type: Cannon 3-pin

Pin 1 GROUND

- Pin 2 INPUT A. Amplitude of 1.4 volts P-P required for full scale conversion.

- Pin 3 INPUT B. Amplitude of 1.4 volts P-P required for full scale conversion.

#### 4.17 ADC DIRECT

Direct input to the Analogue to Digital converter when the ADC DIRECT/ MIC LINE switch is in the ADC DIRECT position. Because this input is Direct Coupled, any D.C. offset on this input will result in a D.C. shift of a sound sample.

Connector Type: Cannon 3-pin.

- Pin 1 GROUND

- Pin 2 GROUND

)

Pin 3 INPUT. Amplitude for full scale conversion is 10 volts P-P.

#### SECTION 5. REPAIR PROCEDURE

Having isolated the faulty sub-assembly, service personel should refer to the service manual for that item for further details.

#### SECTION 6. PREVENTATIVE MAINTENANCE

Under normal conditions, the only preventative maintenance required for the C.M.I. is periodical cleaning of the mesh above the blowers in the Mainframe. Refer to the C.M.I. Mainframe Service Manual for full details. NTS

.

.

CMI\_MAINFRAME\_SERVICE\_MANUAL

## FAIRLIGHT\_INSTRUMENTS, JULY\_1982

:

•

.

```

1

INTRODUCTION

1.1 Card Cage

1.2 Audio Board

1.3 Power Supply

1.4 Floppy-Disk Drives

1.5 External Connections

2

SYSTEM OVERVIEW

2.1 General Principles

2.2 Hardware/Software Relationships

2.2.1 System Startup/Foot

2.2.2 Disk Operations

2.2.3 Graphics Display/Lightpen

2.2.4 Command Entry

2.2.5 Loading/Saving Sounds

2.2.6 Sound Sampling

2.2.7 Music Playing

2.2.8 Music Keyboard Functions

2.2.9 Sequencer

2.2.10 Music Composition Language

3

SPECIFICATIONS

3.1 ELECTRICAL

3.2 AUDIC

3.3 DIGITAL

3.4 MECHANICAL

,4

FUNCTIONAL DESCRIPTION

4.1.1 INTRODUCTION

4.1.2 TIMING & MEMORY CONTROL LOGIC

4.1.2.1 Master Timing Signals

4.1.2.2 Dynamic Merory Timing Signals

4.1.2.3 Data and Address Buss Multiplexing

4.1.2.4 Interrupt Strobe Generation

4.1.2.5 Direct Memory Access

CLCCK DRIVERS, CPUs and VECTOR-FETCH DECODERS

4.1.3

4.1.3.1 Processor Clocks

4.1.3.2 Vector-Fetch Decoders

4.1.4 BUSS DRIVERS & INTERUPT LIVEL MULTIPLEXER

4.1.4.1 Address Buffers/Multiplexers

4.1.4.2 Data Buffers/Multiplexers

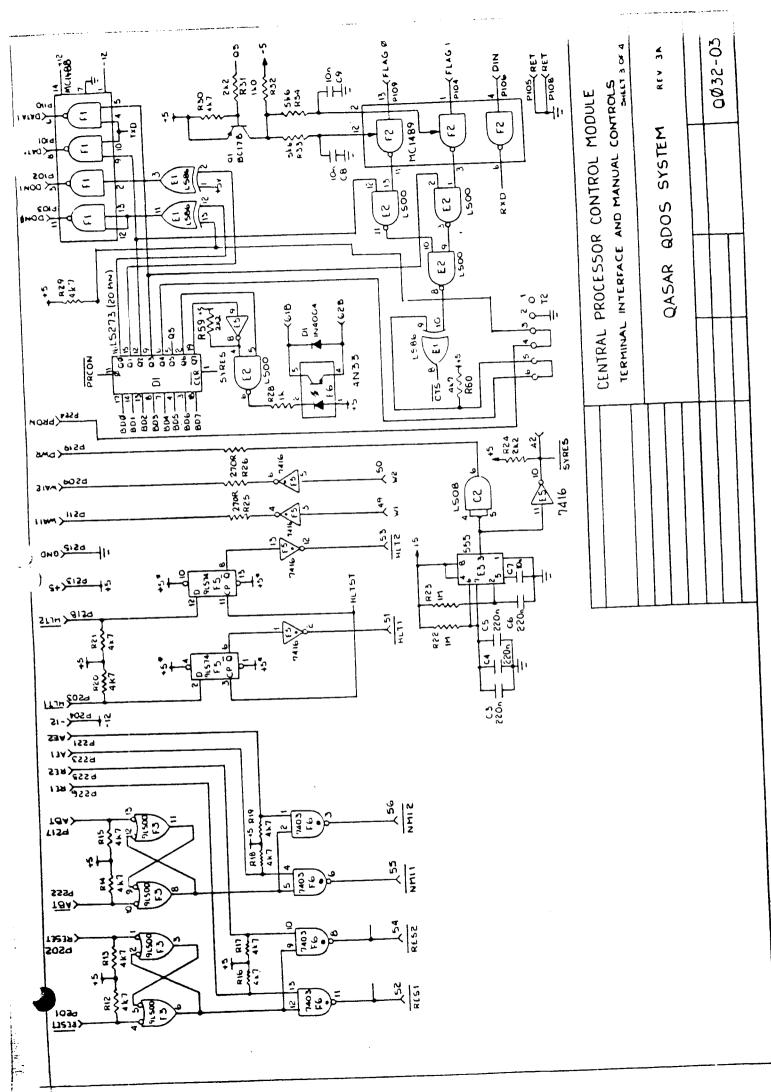

0032 C.P.U. CONTROL CARD FUNCTIONAL DESCRIPTION

4.2

4.2.1 INTRODUCTION

4.2.1.1 Addressing Map

4.2.1.2 Restart and Interrupt Vectors

4.2.1.3 Debug Monitor Firmware

4.2.1.4 System Footstrap/ Disk Controller Firmware

4.2.2 ADDRESS DECCDING AND RAM REFRESH CONTROL

4.2.2.1 Address Decoding

4.2.2.2 RAM Refresh Control

4.2.3 EPRCM, RAM, ACIA, PIA

4.2.3.1 Static RAM

4.2.3.2 EPROM

4.2.3.3 ACIA (Asynchronous Communications Interface Adapter)

18

4.2.3.4 PIA (Peripheral Interface Adapter)

4.2.4 TERMINAL INTERFACE, MANUAL CONTROLS, POWER-CN RESET

```

1

A 2 14

÷,÷

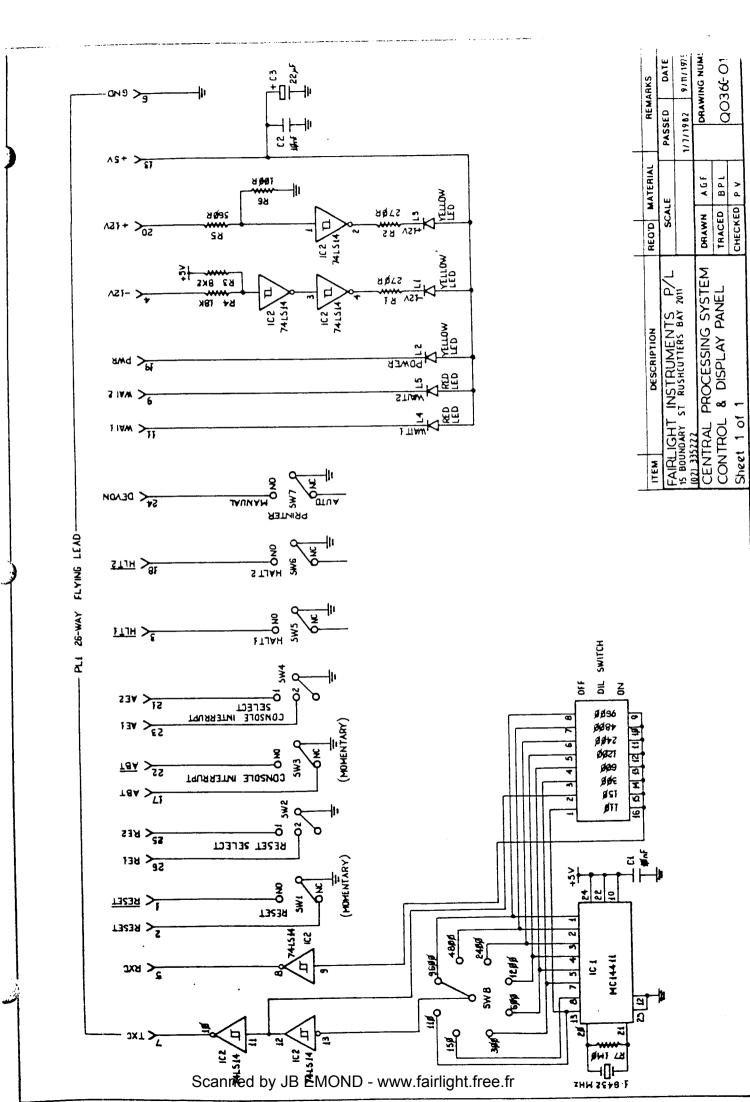

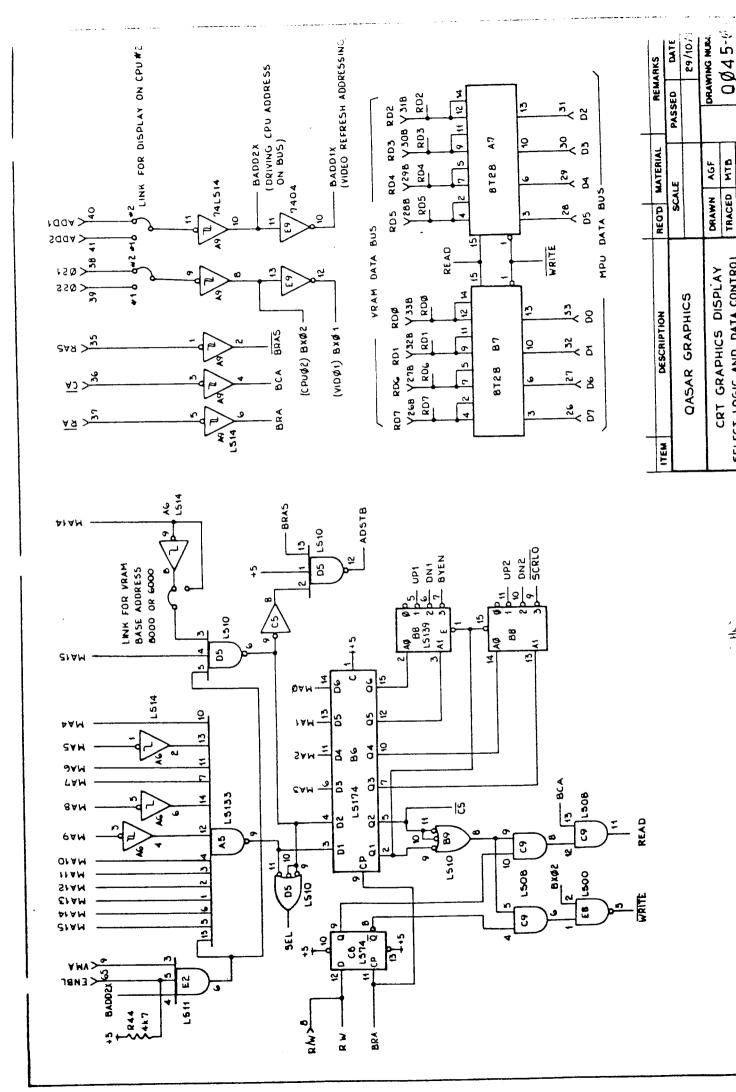

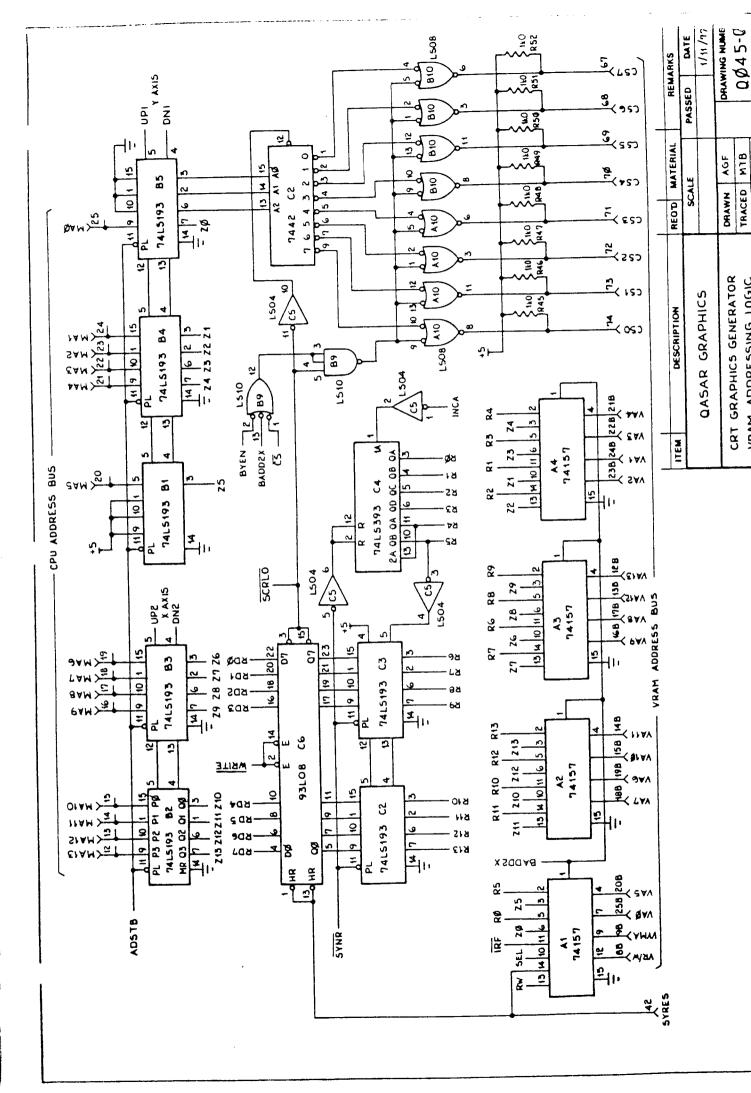

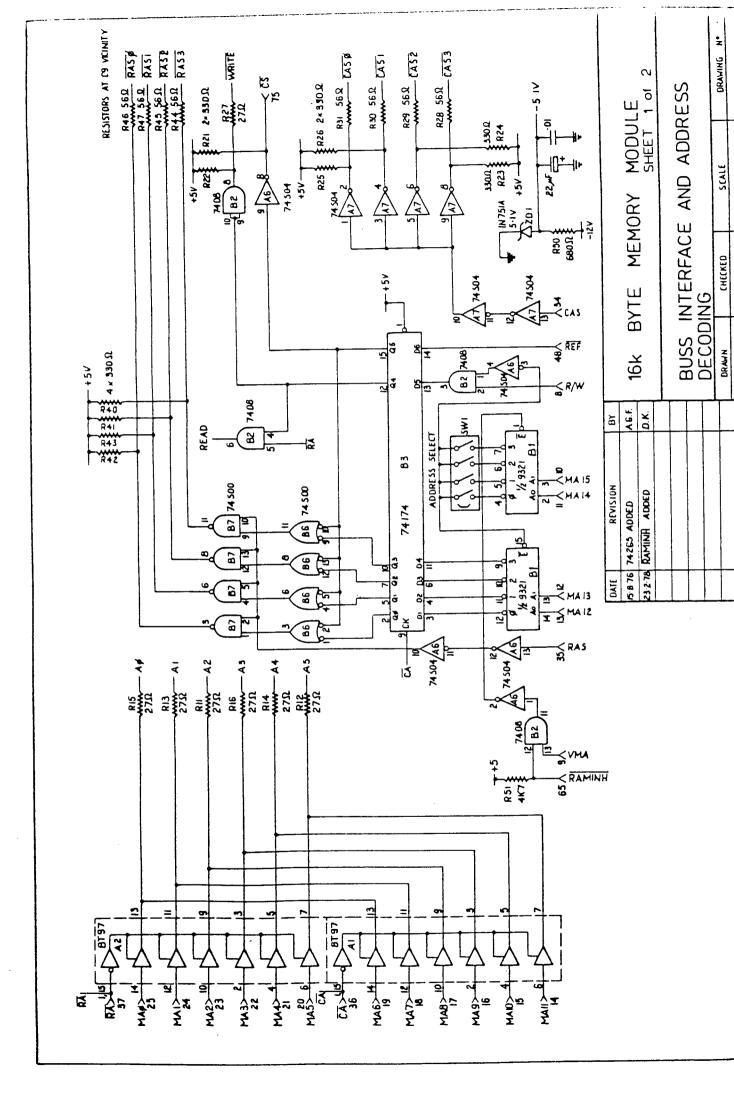

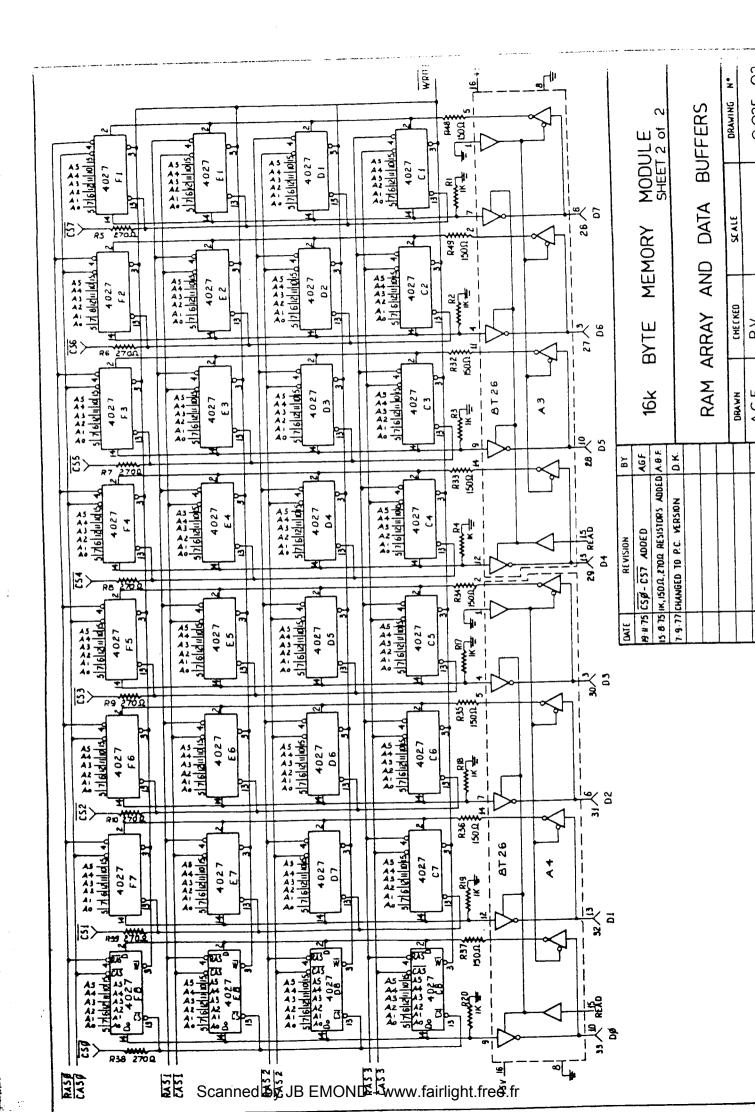

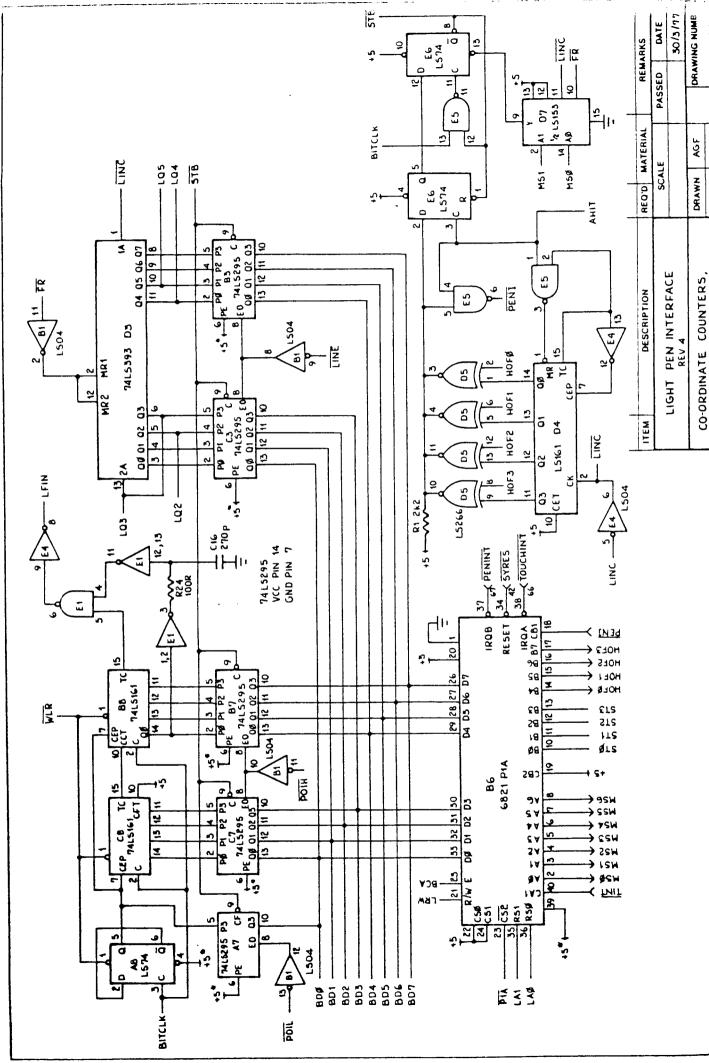

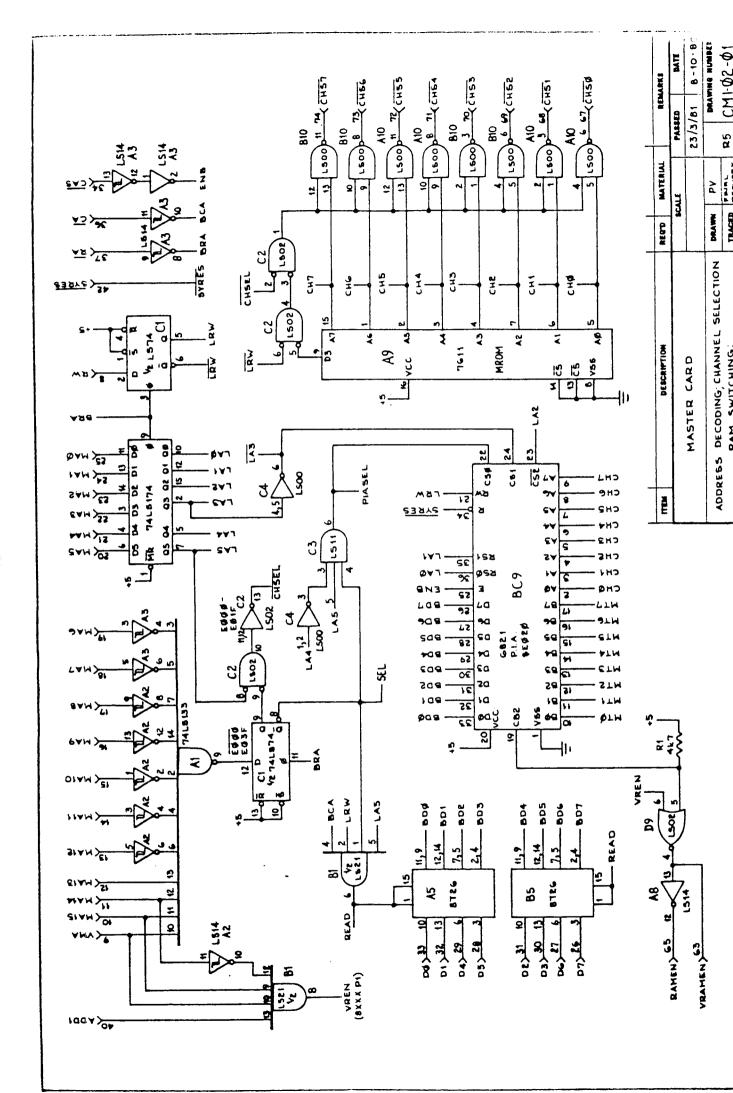

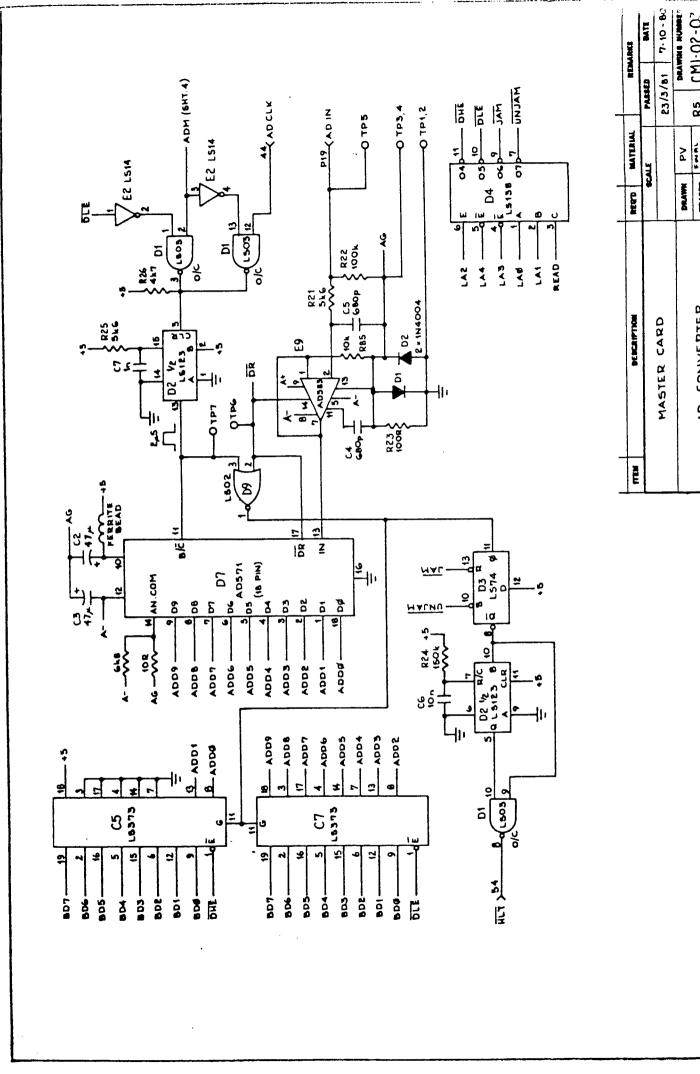

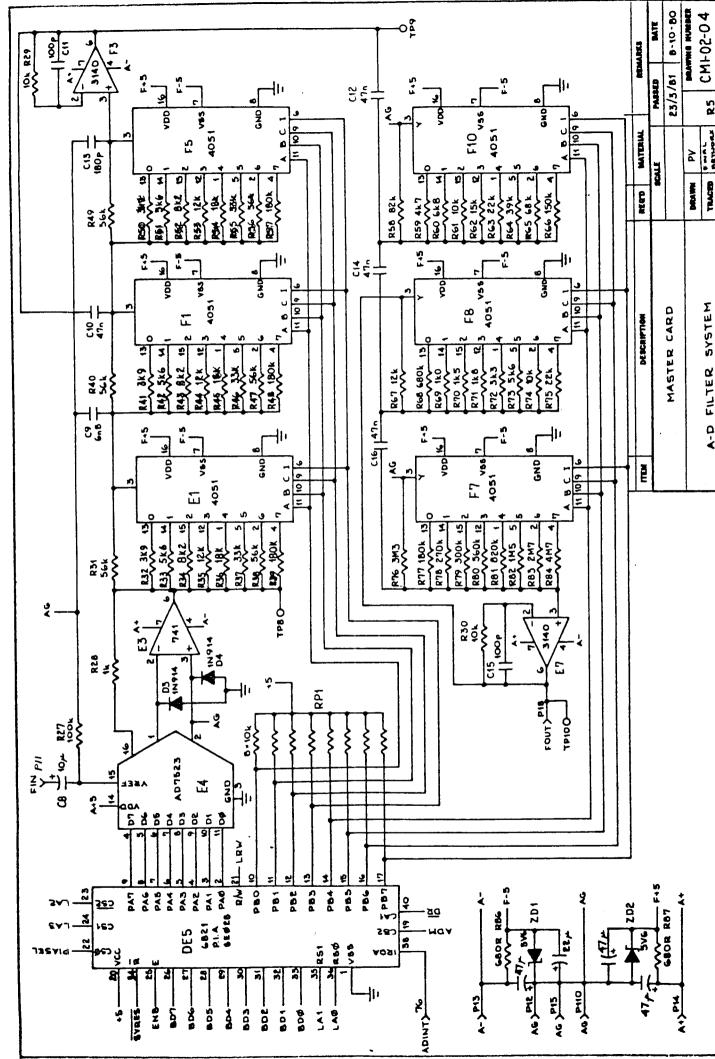

4.2.4.1 Terminal Interface 4.2.4.2. Manual Controls 4.2.4.3 Power-cr Reset 4.2.5 INTERRUPT PPIORITY LOGIC AND DATA BUFFERS 4.2.5.1 Interrupt Priority Logic 4.2.5.2 Data Buffers 4.3.1 INTRODUCTION 4.3.2 ADDRESS DECODING & MAPPING LOGIC 4.3.2.1 Address Decoding 4.3.2.2 Mapping Logic 4.3.3 BUSS INTERFACE 4.3.3.1 Address Buffers and Row/Column Multiplexer 4.3.3.2 DATA BUFFERS 4.3.4 MEMORY ARRAY GFC2 FLOPPY DISK CONTROLLER FUNCTIONAL DESCRIPTION 4.4 4.4.1 INTECDUCTION 4.4.1.1 Address Map 4.4.1.2 Commands 4.4.2 DATA BUFFERS, DMA ADDRESS COUNTER, VERIFY COMPARATOR 4.4.2.1 DMA Address Counters 4.4.2.2 Data Buffers 4.4.2.3 Verify Comarator 4.4.3 ADDRESS DECCIING, CONTROLLER L.S.I., DRIVE SELECT 4.4.3.1 Address Decoding 4.4.3.2 Controller I.S.I. 4.4.3.3 Drive Select 4.4.4 DMA LCGIC 4.4.5 Data Seperator Q045 GRAPHIC DISPLAY CONTROLLER FUNCTIONAL DESCRIPTION 4.5 4.5.1 INTRODUCTION 4.5.2 SYNCE GENERATOR, SEPERATOR AND REGENERATOR 4.5.2.1 Synch Generator 4.5.2.2 Synch Seperator 4.5.2.3. Synch Regenerator 4.5.3 VILEO GENERATION LOGIC 4.5.3.1 Bit Clock Generation 4.5.3.2 Video FIFO and Shift Register 4.5.3.3. Video Cutput 4.5.4 SELECT LOGIC AND DATA CONTROL 4.5.4.1 Address Decoding 4.5.4.2 Data Buffers 4.5.5 VRAM ADDRESSING LOGIC 4.5.5.1 Addressing Counters 4.5.5.2 Bit Selection 4.5.5.3 Vertical Scrolling 4.5.5.4 VRAM Address Multiplexing 4.6 CØ25 16K BYTE MEMORY MODULE FUNCTIONAL DESCRIPTION 4.6.1 INTRODUCTION 4.6.2 ADDRESSING LOGIC & ROW-COLUMN MULTIPLEXER 4.6.2.1 Address Decoding 4.6.2.2 RAS/CAS Generation 4.6.2.3 Row/Column Multiplexers 4.6.3 RAM & DATA EUFFERS 4.6.3.1 RAM Array 4.6.3.2 Lata Buffers 4.7 Q148 LIGHT PEN INTEPFACE - FUNCTIONAL DESCRIPTION 4.7.1 INTRODUCTION 4.7.2 Co-ordinate counters, deglitcher, P.I.A 4.7.2.1 Co-ordinate counters and Latches 4.7.2.2 Hit Leglitcher

1 1 2

1

÷.

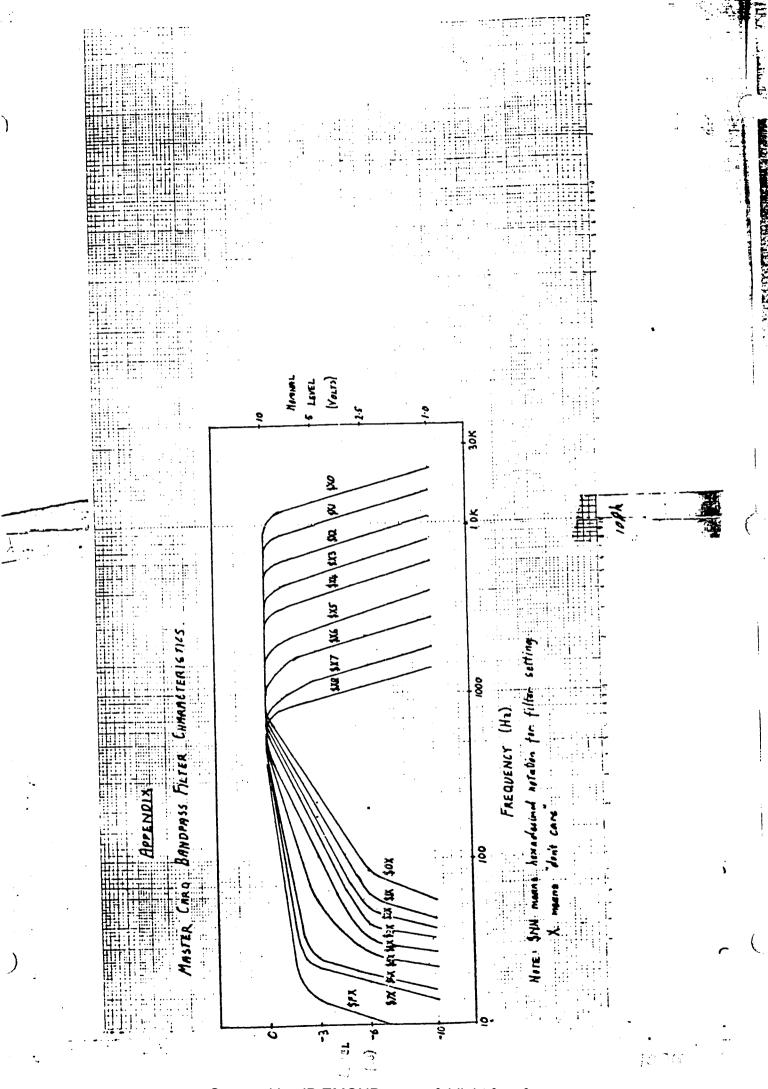

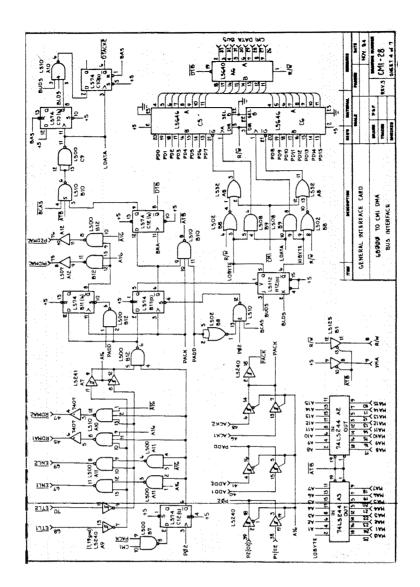

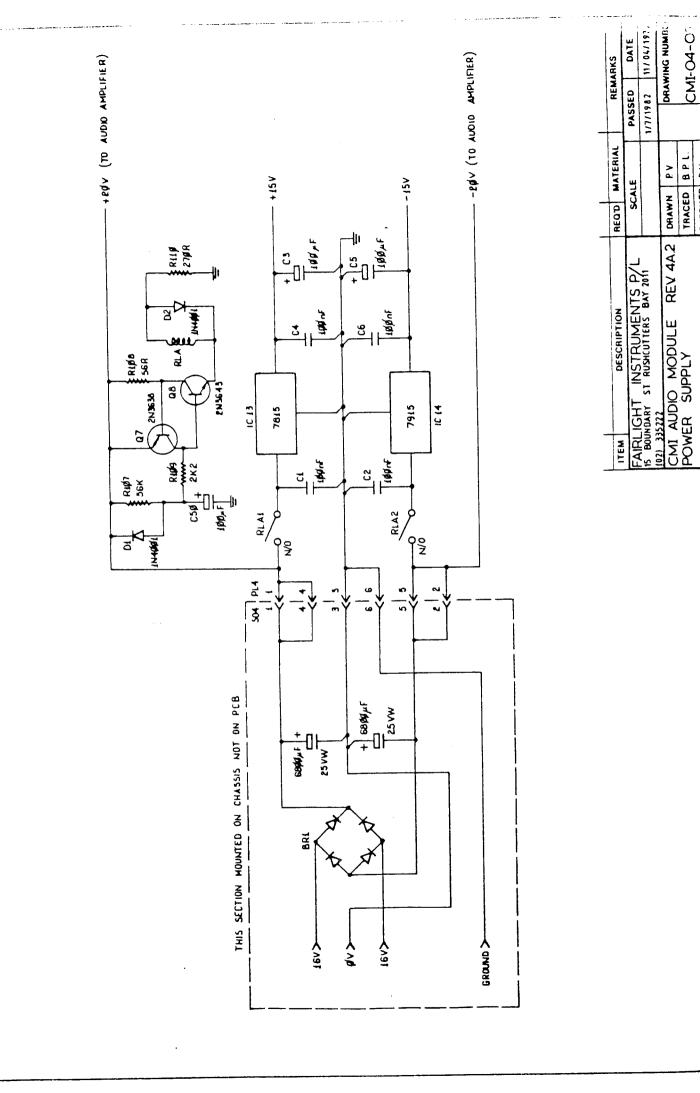

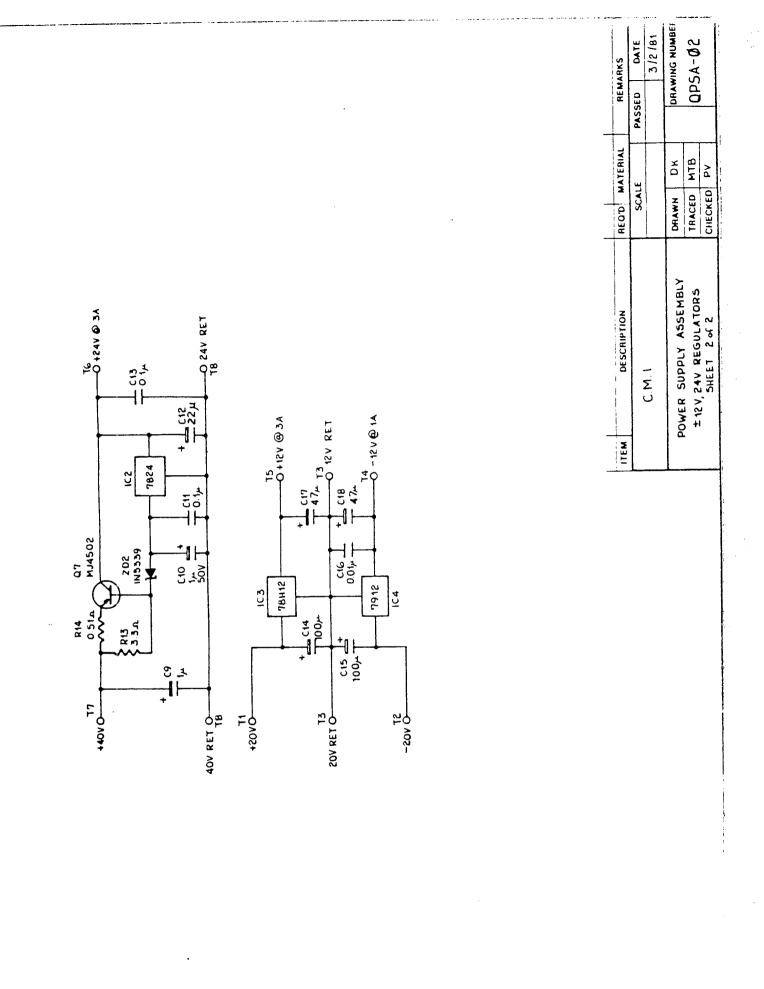

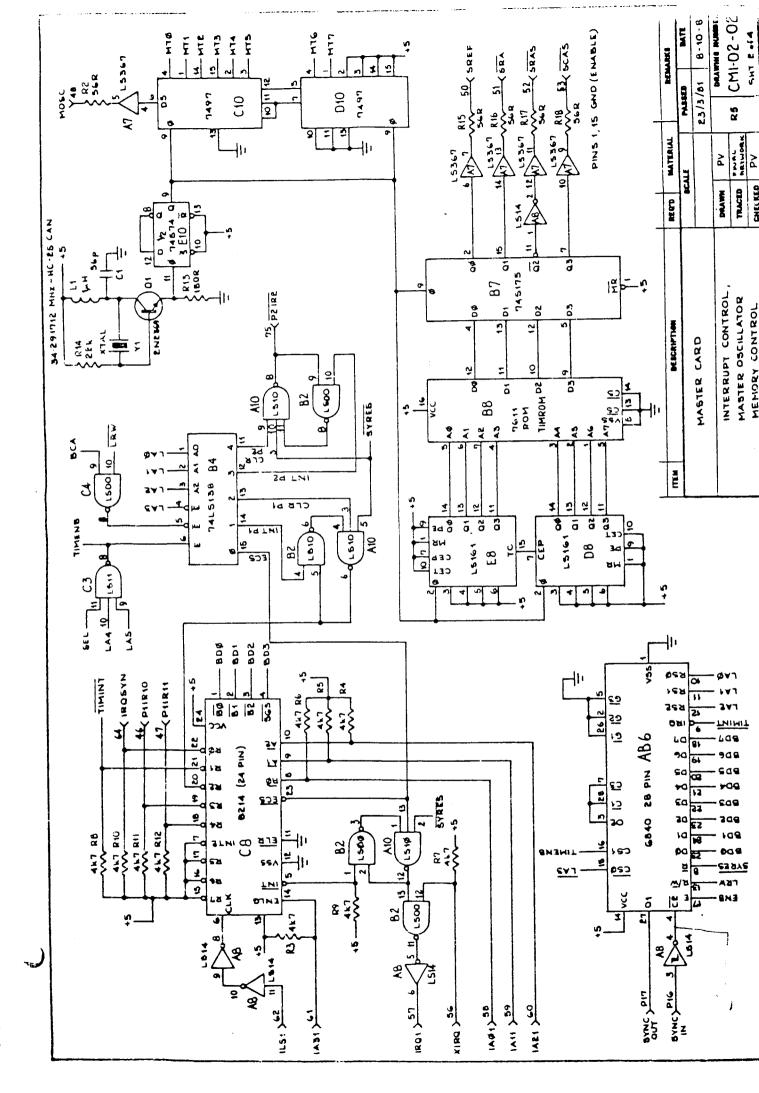

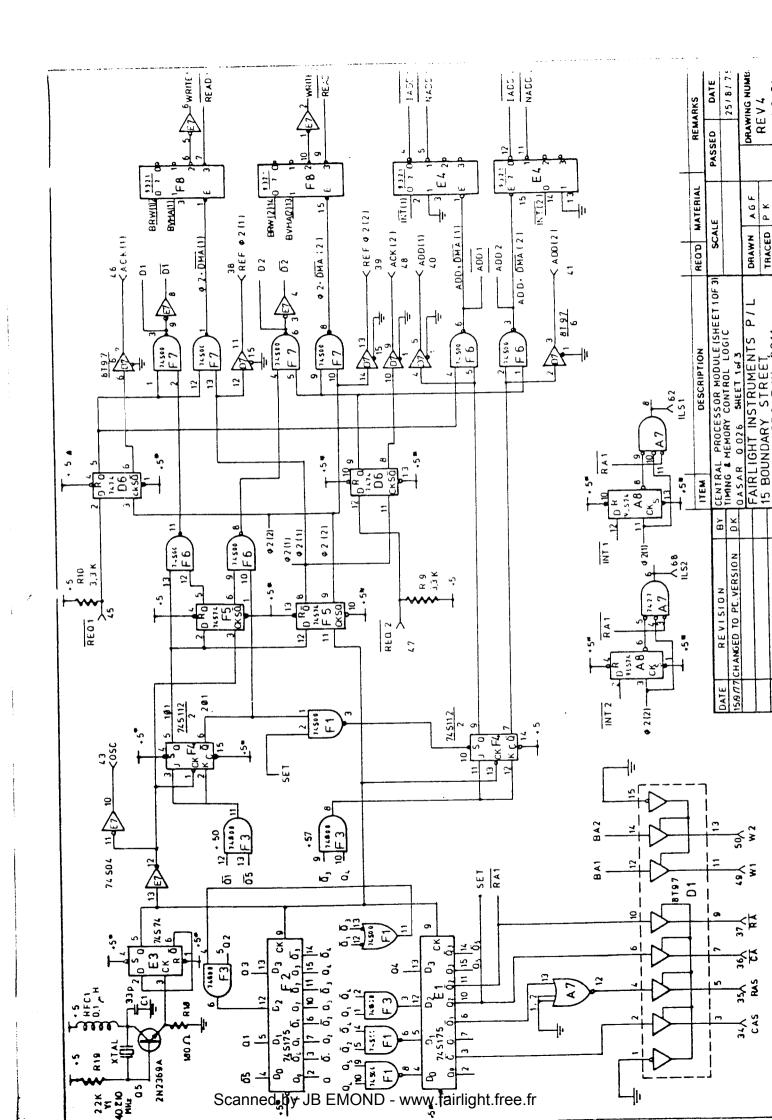

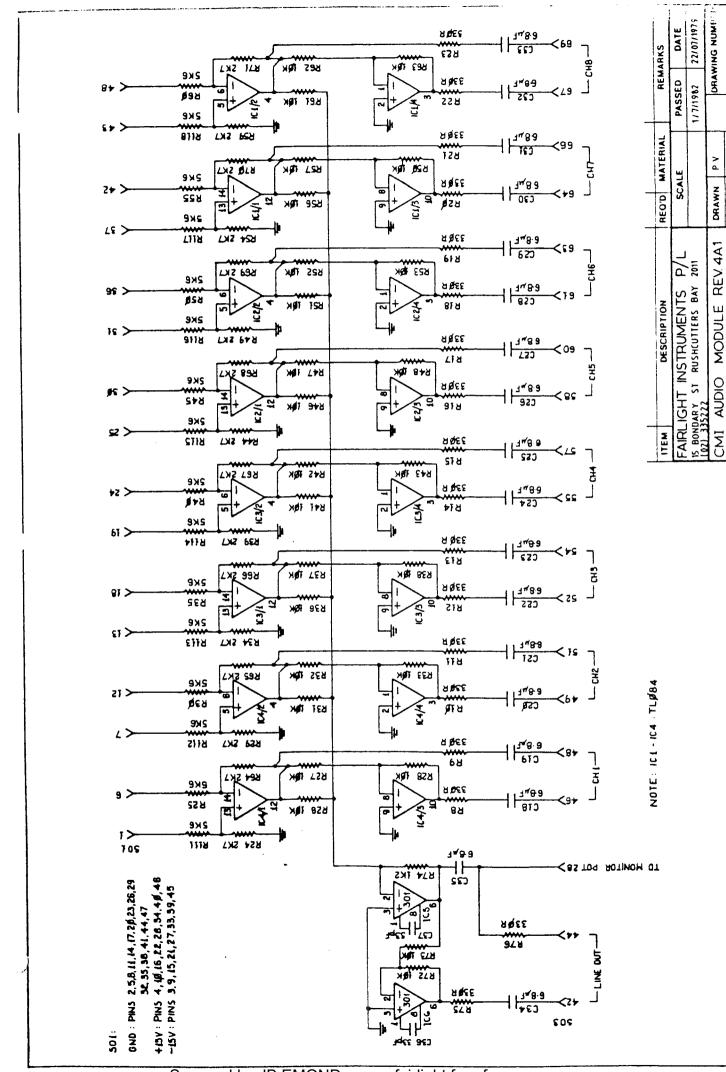

4.7.2.3 Control P.I.A. 4.7.3 Address Decoding, Timer and Lata Buss Control 4.7.3.1 Address Decoding 4.7.3.2 Timer 4.7.3.3 Data Buss Interface 4.7.4 MODE SELECTION AND EXTERNAL SYNCH. 4.7.4.1 Mode Selection 4.7.4.2 External Syrch 4.7.4.3 Hit, Touch Receivers CMIG2 MASTER CARD - FUNCTIONAL DESCRIPTION 4.8 4.8.1 INTRODUCTION 4.8.1 Address Decoding, Channel Selection, VRAM Switching, Master Tuni Register. 4.8.1.1 Address Decoding 4.8.1.2 Channel Selection 4.8.1.3 VRAM Switching 4.8.1.4 Master Tuning Register 4.8.2 Interrupt Control, Master Oscillator, Memory Control 4.8.2.1 Interrupt Control 4.8.2.2 Master Öscillator 4.8.2.3 Memory Control 4.8.3 Analogue to Digital Converter 4.8.4 A-D Filter System 4.9 CMIØ1 CHANNEL CARD - FUNCTIONAL DESCRIPTION 4.9.1 INTRODUCTION CMI04 AUDIO MODULE - FUNCTIONAL DESCRIPTION 4.10 4.10.1 INTRODUCTION 4.10.2 MIXER, LINE DRIVERS 4.10.2.1 Mixer 4.10.2.2 Line Drivers 4.10.3 MONITOR AMP, INPUT AMPS, SYNCE IN/OUT 4.10.3.1 Monitor Amplifier 4.10.3.2 Input Amplifiers 4.10.3.3 Synch In/Out 4.10.4 POWER SUPPLY 4.11 QPSA D.C. POWER SUPPLY ASSEMBLY - FUNCTIONAL DESCRIPTION 4.11.1 INTROIUCTION 4.11.2 UNREGULATED SUPPLIES 4.11.3 REGULATOR 5 VCLT 18 AMP 4.11.4 ± 12 VOLT, 24 VOLT SUPPLIES 4.12 Q036 FRONT PANEL CONTROL 5 TROUBLESHCOTING 5.1 Introduction 5.2 Power Supply 5.3 Corputer Section 5.4 Disk System 5.5 Channel Cards 5.6 Master Card 5.6.1 Channel Card Selection 5.6.2 Channel Card Master Clock 5.6.3 Analogue to Digital Conversion 5.6.4 External Synchronisation and Timer 5.7 Audio Card DIAGNOSTIC SOFTWARE 6 6.1 INTRODUCTION TO DIAGNOSTIC SOFTWARE 6.1.1 Running the Diagnostic Disc 6.1.2 Running the Test Programs 6.1.3 Measurement Tolerances

$\mathbf{\tilde{s}}$

6.2 Channel Card Tests 6.2.1 Filter Tests 6.2.2 Waveform Memory Tests 6.2.3 Envelope Control Tests 6.2.4 Volume Control 6.2.5 Timer Tests 6.2.6 Pitch and Octave Control 6.2.7 Interrupt Flags 6.3 Master Card Tests 6.3.1 Timer Tests 6.3.2 Master Fitch Register Test 6.3.3 A-I Converter System Tests 6.3.3.1 AD Tests using External Analog Source 6.3.3.2 AD Tests Using Internal Analog Source 6.3.4 Master Fandpass Filter Tests 6.3.5 Video Ram Control 6.4.0 64% RAM Card Tests 6.4.1 MEMTST 6.4.2 MEMCH 6.5.0 Central Processor Control Module 6.6.0 Light Pen Interface 6.1 CMILP 6.6.2 LPTST 6.6.2.1 Light Pen Timers 6.6.2.2 Light Pen PIA 6.6.2.3 Processor Access Selection 6.6.2.4 Light Pen Drawing 6.7.0 Graphics System 6.8.7 Floppy Lisc Controller 6.8.1 FDCFIX 6.8.2 FDCIMA 6.8.3 QFC-2 Alignment 6.9.0 Interrupt Tests - CMIINT 6.10.0 Testing a Complete CMI - Chain Tests 6.10.1 Digital System Tests 6.10.2 Channel Card Analogue Tests 6.10.3 Comprehensive Analogue Test 6.11.0 Summary of Test Waveforms 6.11.1 CMITST 7 SIGNAL LIST - MOTHERBOARD 7.1 Master Card CMI-02 - Slot 1 7.2 Channel Card CMI-Ø1 - Slots 3 to 10 7.3 Analog Interface Card CMI-07 - Slot 11 7.4 Light Pen Interface Q148 - Slot 12 7.5 64K System RAM Q-096 - Slots 13 to 15 7.6 Processor Control (CØ32) Module C-Ø32 - Slot 16 7.7 Central Processor Module Q-026 - Slot 17 7.8 Floppy Disc Controller QFC-2 - Slot 18 7.9 Graphics Controller Q-045 - Slot 9 7.10 16K Graphics RAM Q-025 - Slot 20 8 SIGNAL LIST - EXTERNAL CONNECTIONS 8.1 A.C. Mains 8.2 Graphics Power 8.3 Graphics 8.4 Keyboard Power 8.5 Keyboard 8.6 Printer 8.7 Phones

1

-----

÷

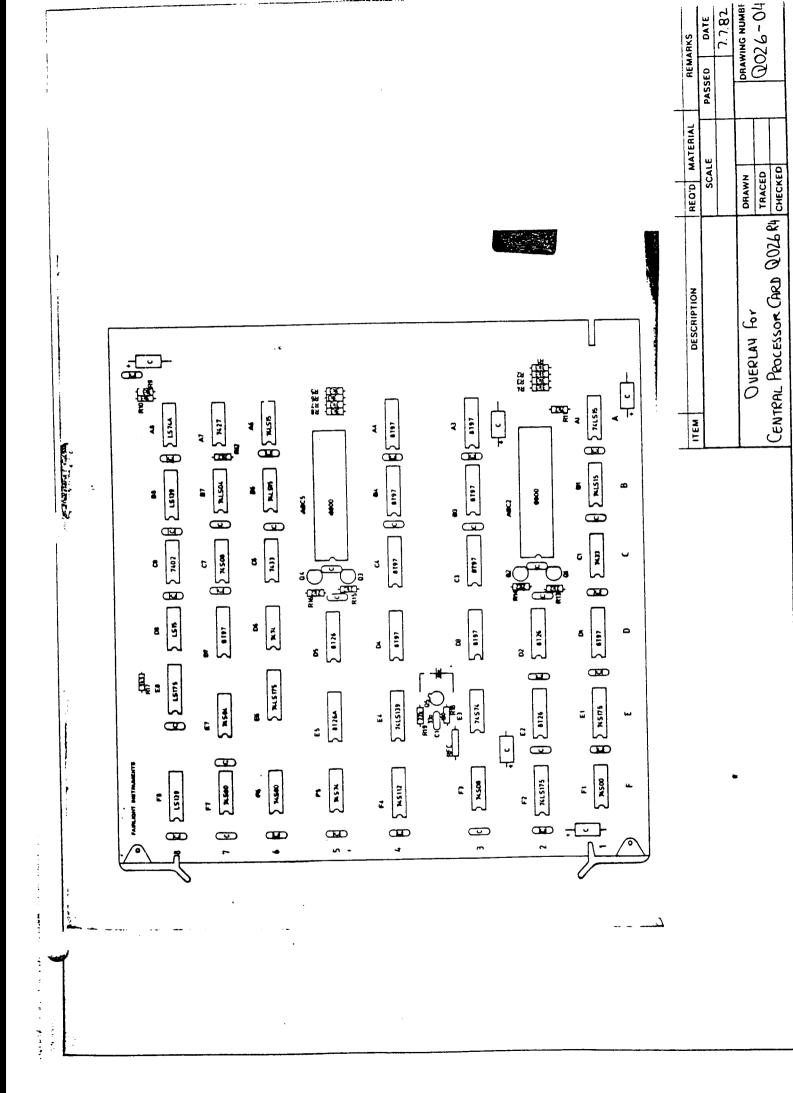

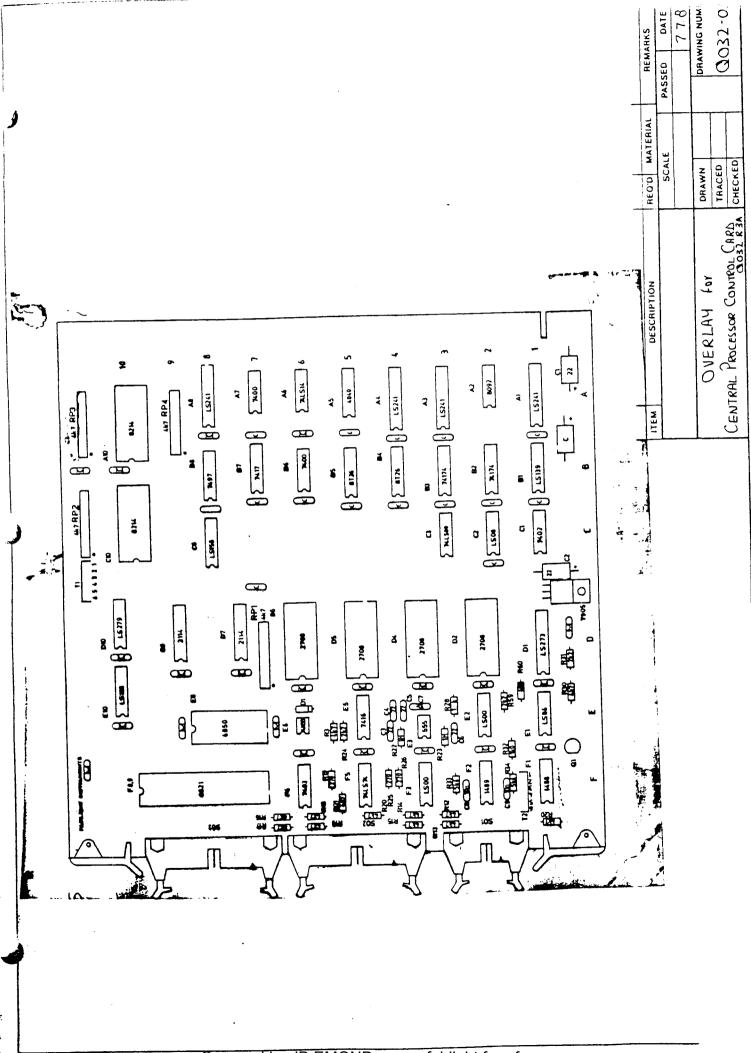

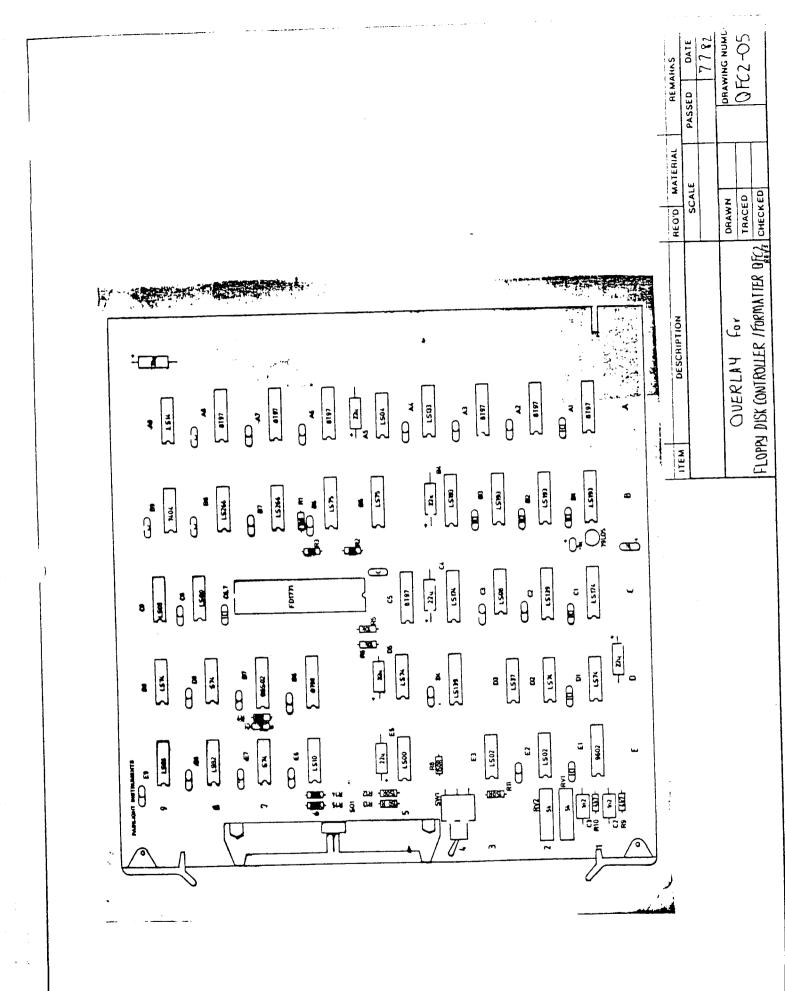

8.8 Monitor 8.9 Channels 1-8 8.10 Mixed Line Output 8.11 Sync 8.12 Filter Out 8.13 Mic In 8.14 Line In 8.15 ADC LIRECT g REMOVE/REPLACE PROCEDURES 9.1 CIRCUIT EOARE REMOVE/REPLACE 9.2 DISK DRIVE REMOVE/REPLACE 9.3 REAR FANEL REMOVE/REPLACE 9.4 AUDIO BOARI CMI-04 REMOVE/REPLACE 9.5 FAN ASSEMBLY REMOVE/REPLACE 9.6 MOTHERBOARD CMI-05 REMOVE/REPLACE S.7 POWER SUPPLY REGULATOR REMOVE/REPLACE S.8 D.C. SUPPLY REMOVE/REPLACE 9.9 CARD CAGE REMOVE/REPLACE 10 REPAIR PROCEFURE 11 PREVENTATIVE MAINTENANCE 12 SCHEMATIC DIAGRAMS 12.1 Q026 SCREMATIC 12.2 QØ32 SCHEMATIC 12.3 Q096 SCHEMATIC 12.4 QFC2 SCHEMATIC 12.5 Q045 SCHEMATIC 12.6 0025 SCHEMATIC 12.7 C148 SCEEMATIC 12.8 CMI02 SCHEMATIC 12.9 CMI01 SCHEMATIC 12.10 CMI04 SCHEMATIC 12.11 QPSA SCHEMATIC 12.12 QØ36 SCHEMATIC 13 CIRCUIT BCARD OVERLAYS Q026 OVERIAY 0032 OVERIAY 0096 OVERLAY QFC2 OVERLAY 0045 OVERLAY 0025 CVERIAY Q148 OVERLAY CMIØ2 OVERLAY CMIØ1 OVERLAY CMI04 OVERLAY OPSA OVERLAY 0036 OVERLAY 14 ELECTRICAL PARTS LISTS 14.1 Q026 DUAL 6800 PROCESSOR 14.2 QØ32 PROCESSOR CONTROL CARD 14.3 Q096 64K RAM CARD 14.4 QFC2 FLOPPY DISK CONTROLLER 14.5 CØ45 GRAPHICS CARD 14.6 Q025 16K RAM CARD 14.7 Q148 LIGHT PEN CARD 14.8 CMI 02 MASTER CARD

• • • • •

ł

1

|    | 14.9 CMI01 CHANNEI CARD<br>14.10 CMI 04 AUDIO CARD<br>14.11 GPSA REGULATED POWER SUPPLY<br>14.12 Q036 FPONT PANEL CONTROL CARD                                                                                                                                                                                                                      | 173<br>17<br>18<br>18                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

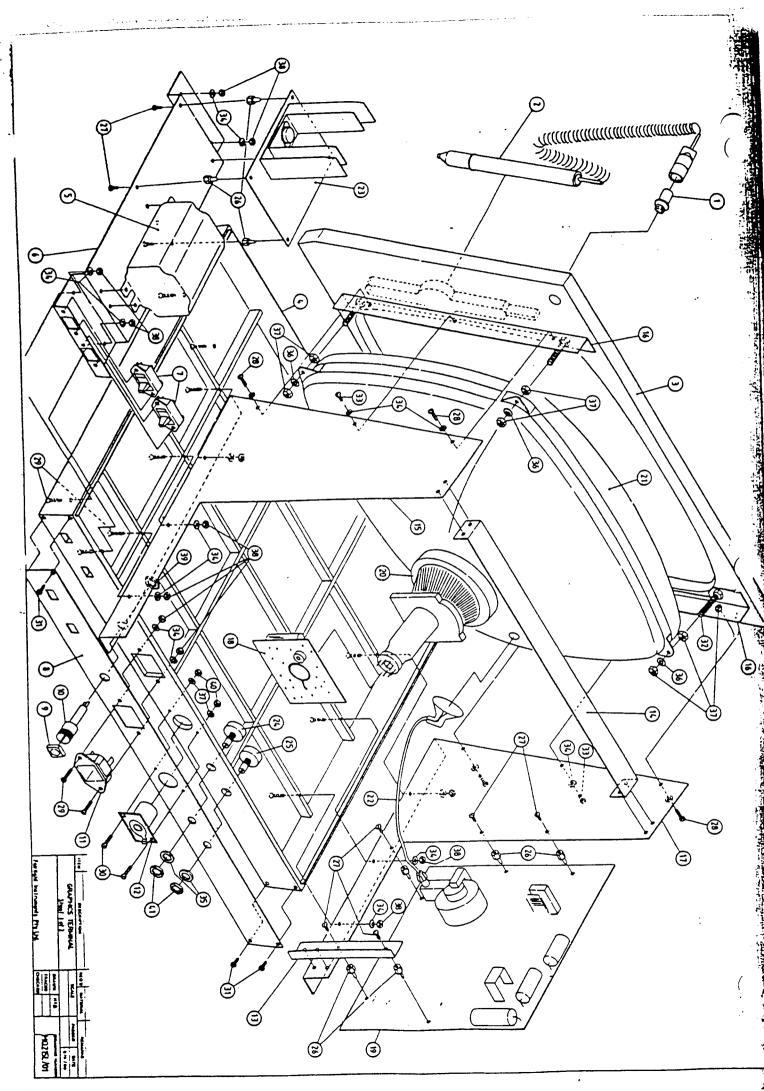

|    | MCG01-01 WIRING LIAGRAM<br>EXPLODEL VIEWS<br>16.1 DMC046 TEANSFORMER END PLATE<br>16.2 IMC032 CARE CAGE ASSEMBLY<br>16.3 DMC057 REGULATED POWER SUPPLY<br>16.4 DMC066 FAN ASSEMBLY<br>16.5 IMC038 REAR PANEL<br>16.5 IMC038 REAR PANEL<br>16.6 IMC042 FRONT PANEL<br>16.7 DMC001 MAINFRAME                                                          | 18<br>18<br>18<br>18<br>18<br>18<br>18<br>18<br>19 |

| 17 | MECHANICAL PARTS LISTS<br>17.1 C.M.I MAINFRAME DRAWING REF.LMC0001<br>17.2 CARD CAGE ASSEMBLY DRAWING DMC032<br>17.3 MAINFRAME REAR PANEL DRAWING DMC038<br>17.4 FRONT PANEL ASSEMBLY DRAWING DMC042<br>17.5 TRANSFORMER END PLATE DRAWING DMC046.<br>17.6 REGULATED P.S.U ASSEMBLY DRAWING IMC027<br>17.7 FAN ASSEMBLY FAN ASSEMBLY DRAWING DMC066 | 19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19 |

Ŧ

· •

> н 1. 19 1. 19

•

.

## 1.0 INTRODUCTION

<u>,</u>

3

)

4 3

· · · · · · ·

The C.M.I. Mainframe houses all the data processing and audio genneration hardware of the C.M.I. System, including E.C. power supplies and floppy-disk drives.

This manual is designed to help service personel locate and rectify a fault in the C.M.I. mainframe.

Note that this manual only refers to the Mainframe itself. The remainder of the C.M.I. System is covered by the following related docurents:

C.M.I. SYSTEM SERVICE MANUAL MUSIC KEYEGARD SERVICE MANUAL ALPHANUMERIC KEYBOARD SERVICE MANUAL GRAPHICS TERMINAL MAINTENANCE MANUAL DISK DRIVE MAINTENANCE MANUAL

1.1 Card Cage

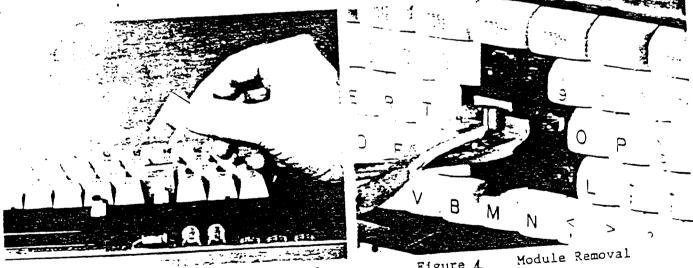

A 21-slot card cage houses a printed-circuit motherboard carrying edge connectors into which the C.M.I. circuit boards are inserted. The cards can be accessed by hinging down the front panel, and they can removed from the front of the unit without requiring the use of any tcols.

1.2 Audio Board

Cables from the front of each channel card connect to the audio toard located inside the rear panel of the mainframe. This card supports a variety of audio functions, including balanced line drivers for the eight channels and mixed output.

This card is accessed by removing the four mounting screws securing the rear panel and swinging the panel down. The card itself is held in place by screws. All connections are made by plug-in cables.

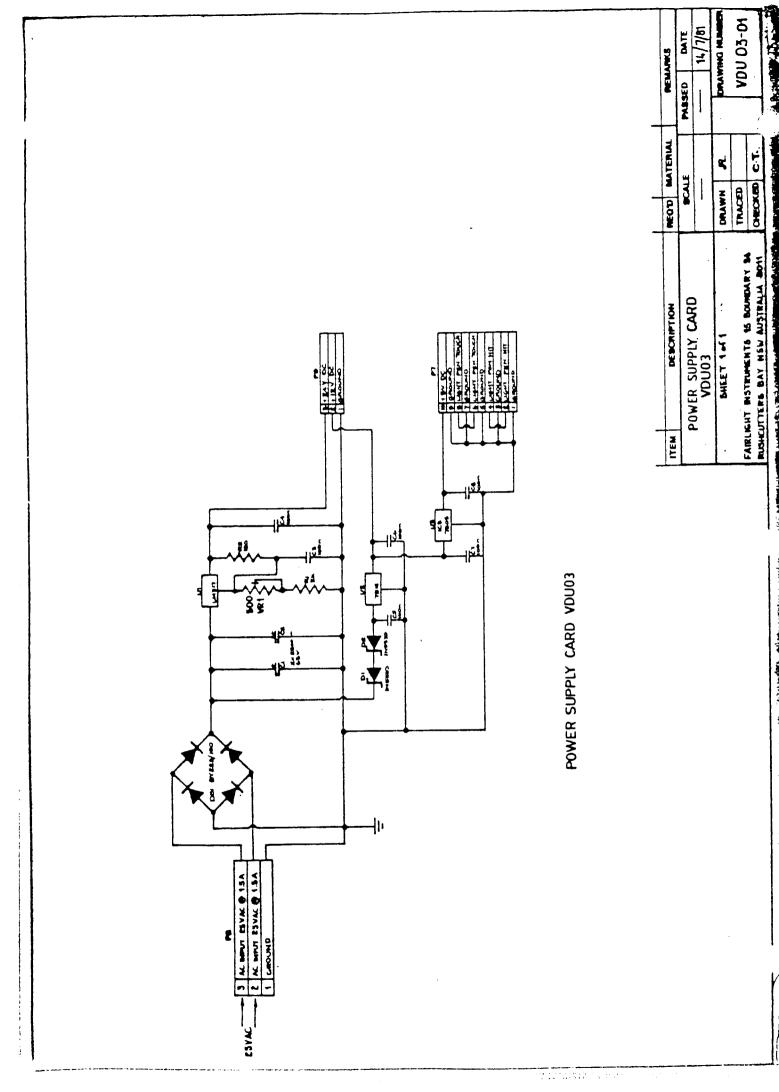

1.3 Power Supply

D.C. power is provided by a conventional transformer/rectifier system mounted inside the left-hand end of the card cage. This supplies power for the card cage, audio board, floppy-disk drives, music keyboard and alpha-numeric keyboard.

1.4 Floppy-Disk Drives

Two eight-inch, double sided, single density disk drives are mounte to the right of the card cage. They connect to the power supply via wiring harness and to the floppy-disk controller card in the card cag via a 50-way ritton cable.

.

Scanned by JB EMOND - www.fairlight.free.fr - OTRUTOR MANUAL - Page

1.5 External Connections

1

)

**?** -

All external connections are made by means of plug-in cables. The mainframe is normally connected to A.C. mains, Graphics Terminal Music Keyboard and audio equipment such as monitor speaker or mixin console.

The precise function of each external connection is described unde Signal Lists (below).

2.0 SISIEM\_OVERVIEW

2.1 General Principles (Refer to Figure 1)

The C.M.I. is a complex special-purpose computer system which embrace many different hardware and software technologies. All processing an sound generation functions are performed by the Mainframe, while th Graphics Terminal and Keyboards serve as peripherals for operato interfacing.

The mainframe is capable of operating quite autonomously, that is, i is not reliant on any external connections for proper funtioning Under certain conditions it is possible for a fault condition t inhibit proper Mainframe operation, so the serviceman should be war of being misled. Of course, without the peripherals connected it i often hard to know if the system is functioning properly, but thi point should be borne in mind when troubleshooting.

Cperator input to the Mainframe comes from three sources: rusi keyboard, alpha-numeric keyboard, and lightpen. Output devices includ the Graphics Display terminal, and the audio outputs. A printer ma also be optionally used.

The heart of the system is the Central Processor Module, which use two Motorola 6800 microprocessors in a dual-processor configuration Both processors share a common buss which allows them both t communicate with the other cards in the Mainframe.

The Processor Control Module provides EPROM for system startup an bootstrap, RS-232 serial input from the keyboard, serial output to th keyboard and printer, and various other C.P.U. support functions suc as interrupt prioritisation.

Main programme memory is the 64 kilobyte RAM card. This holds all th operational software, much of which is overlayed from disk as the cod far excedes 64 K.

The floppy-disk controller uses Direct Memory Access techniques t transfer data between memory and the two flopp-disk drives.

The Graphics Display is a bit-mapped image of 16 kilobytes of VRAM The Graphics Controller module displays this RAM as an array of 256 512 points. Special hardware on this card provides support function for automatic vector drawing, which considerably enhances the speed o displaying graphical information.

C.M.I. MAINFRAME SERVICE MANUAL - Page 2

The Lightpen Controller module interfaces the Hit and Touch signal from the Lightpen (part of the graphics display terminal) to th system buss.

Eight identical Voice Modules also share the bus. They each have 1 kilobytes of waveform RAM, as well as all the control and audi circuits required to support it.

A Voice Master module controls the voice modules, as well as providin the Analogue to Digital converter function of the system. Audio from the Voice Modules is buffered by the Audio Cutput Module which provides indepenant balanced outputs for each channel as well a a mixed output.

)

Scanned by JB EMOND - www.fairlight.free.fr

Figure 1. C.M.I. SYSTEM BLOCK DIAGRAM

#### 2.2 Hardware/Software Relationships

This section gives a summary of the operational concepts involved i each of the C.M.I.'s major functions. This information should hel relate a particular software function to the appropriate piece of hardware.

The software system is divided into two main sections, the resident software and overlays. The resident part is responsible for all the real-time functions such as sound generation, keyboard inpuprocessing and lightpen operation. The overlays are used for the various control and sound manipulation functions provided by the display pages. Changing pages on the C.M.I. loads a new overlay for that page from disk. Some pages use further overlays themselves, so that when certain functions are invoked from a particular page for the first time, a disk access will be made as the overlay is loaded.

Both processors have access to the 64 kilobytes of program R.A.M., s that some of the code may be executed by each processor individually and both processors can share common data structures. As a rule processor 1 is responsible for controlling the voice modules (channe cards) and handling data from the keyboard. Processor 2 carries ou the non-realtime functions such as disk I/C and graphics display.

A broad description of a range of specific functions follows.

2.2.1 System Startup/Boct

)

When power is first applied to the system, a power-on reset signal i generated for about a half second by a timer located on the Processo Control card, Q032. At the end of this time, both processors fetc restart vectors from EPROMS, also on the Q032 card and start executin the startup procedure in EPROM. Processor 1 initialises all th registers of the peripheral controller devices such as P.I.A.s an A.C.I.A.s. Processor 2 initialises the Graphics Display, clears th screen, and displays the "C.M.I. READY" message. The same message i sent to the music keyboard display via the serial link on the Q03 card. Processor 1 then loops waiting to be triggered by processor 2 which in turn loops waiting for a disk to be inserted in drive 0, a indicated by the appropriate status bit from the floppy-dis controller card QFC2.

When the sysytem disk has been correctly inserted, processor executes the first stage of the bootstrap loader firmware (located o the Q032 card). This involves reading in the boot block, which is special sector on the system disk. The code stored in the boot bloc is then executed, which completes the boot load by loading th operating system and the Page 1 overlay. When Page 1 starts up, th message Page 1 ready is sent to the music keyboard display.

2.2.2 Disk Operations

The C.M.I. uses two eight-inch double-sided disk drives. Format i soft sectored, 128 bytes per sector. Single density FM recording i used for extra reliability.

C.M.I. MAINFRAME SERVICE MANUAL - Page 5

The drives themselves are controlled by a Western Digital FD1771 L.S.I. controller located on the Floppy Disk Controller Card QFC2.

The disk driver EPROM located on the C232 card is used as the lowest level disk driver. Routines in this EPROM provide utilities including read sector, write sector, and verify C.R.C. which are called by the RAM-resident disk-operating system.

In the event of a disk error being detected during a read or write operation, the software will perform a number of retries, including head relocation, to try to recover from the error. If the error persists, a DISK READ/WRITE error message is displayed.

2.2.3 Graphics Eisplay/Lightpen

•••

Ż

)

The graphics display is generated by writing a bit-mapped image to the dedicated 16 kilotyte VRAM. This block of RAM is mapped in and out of the processor memory space under software control. The register for this purpose resides on the Master Card CMI02 (see functional description below).

The lightpen is interfaced via the Q148 Lightpen Interface card, and an interrupt to Processor 2 is generated each time the light pen Touch and Hit signals are asserted simultaneously. The processor 2 resident code is then executed to poll the lightpen co-ordinate registers and the appropriate action ensues.

The lightpen cursor is a hardware function (see Q148 functional description below).

2.2.4 Command Entry

Data arriving from the Music Keybcard is fed to the A.C.I.A. on the 0032 Processor Control Card. The A.C.I.A. generates an interrupt of processor 1 for as each byte is assembled. Data from the music keyboard and characters from the alphanumeric keyboard both arrive a the same A.C.I.A. They are distinguished by the fact that music keyboard data has the high bit set. Data from the Music Kekboard arrives in the form of three-byte packets. These are assembled and queued by processor 1 for playing. Alphanumeric characters are passed on to processor 2. This is done via common memory and an inter processor interrupt. Interprocessor interrupts are generated b special hardware located on the Master Card CMI02 (see functiona description below).

#### 2.2.5 Loading/Saving Sounds

Sounds are stored as contiguous "Voice" files on disk. Each voice fil occupies about 20 kilobytes of disk space. An entry in the director on track zero gives the physical sector number of the start of th file. When a file is loaded, the directory is searched and the addres of the file found. The sound is then loaded one sector at a time Since processor 2 performs all disk operations and processor controls the channel cards, data is passed between the processors vi a buffer in common memory. If more than one channel is being loaded with the same sound, multipl channels are enabled by the Master Card so that they can be written t simultaneously. See Master Card Functional Description (below) fo full details.

Saving sounds operates by the reverse process.

2.2.6 Scund Sampling

----

. . \*

)

Audio input for sampling is fed to either the line input or mic input connector on the rear panel. It is amplified on the Audio Card CMIG and then fed to the Master Card CMIØ2 via a 10-way ribbon cable. The signal is then attenuated by a digitally controlled attenuator and filtered by seperate low pass and high pass filters on the Audio Card These filters are also software controllable. The attenuator is controlled by the Level control on Page 8 of the CMI system software and filter cutoff points are controlled by the Filter High and Filte Low controls.

From the filters the audio is fed to the Analogue to Digital converter. The sample rate is governed by the frequency of a puls stream coming from the Channel Card in channel one position. The sample rate is therefor established by software which sets up channel one to operate at the frequency specified as sample rate on Page 8.

Processor one is used to read data from the A-D converter and store is in the desired channel cards' waveform R.A.M. To synchronise th processor with the converter, processor one is forced to a Halt stat while a conversion is in progress, and as soon as the conversion is complete and data is ready to be read, the processor is un-halted and it reads the data. This causes Processor one's Halt L.E.D. to glo while conversions are in progress.

The Trigger Level function on Page 8 is purely a software function When the Sample command is issued, the processor starts conversion and loops until the data read is of a greater absolute value than th rumber specified as trigger level. It then begins transferring data t the Waveform R.A.M.

2.2.7 Music Playing

Data arriving from the music keyboard is seperated from alphanumeri keyboard strokes and assembled into three byte packets by Processor (see 2.2.4 above). The A.C.I.A. routine is interrupt driven. Once three-byte music keystroke packet has been assembled, the require note is played or stopped. The packet gives the keyboard number whether the stroke was a depression or a release, and a key velocit number.

Once the correct channel or group of channels has been identified by software relating to the keyboard/register map on Page 3, they ar started by the appropriate sequence of software commands. The channe cards generate a number of interrupts as the sound progresses an various paarmeters need to be updated.

Parameters fed to the channel card specify the pitch of the channel instantaneous amplitude, amplitude change (automatic ramping up o down), and position within the waveform.

C.M.I. MAINFRAME SERVICE MANUAL - Page 7

The audic out put from each channel card is fed to the audio card by a 10-way ribbon cable plugged into the front of the card.

2.2.8 Music Keytoard Functions

As well as sending music key depression/release data to the mainframe, the music keyboard has a number of ancillary functions.

A multiplexed analogue to digital converter samples the level of the three faders on the left-hand end of the keyboard as well as the three pedal inputs on the rear. Whenever one of these changes its level by more than a certain amount, a packet of data is transmitted to the mainframe, giving the device number and the new level.

The two switches on the left of the keyboard and the three switches which plug into the rear of the keyboard are also scanned, and when any of these are opened or closed, suitable data is sent to the Mainfrage.

Pressing a key on the numeric keypad on the right end of the keyboard sends a character to the Mainframe in exactly the same way as an alphanumeric key depression.

The alhphanumeric L.E.D. display on the music keyboard is driven by the serial lirk coming from the Mainframe. The processor in the keyboard controls the displaying of individual characters as well as backspace and clear. When messages longer than the 12 digits of the display are required, a horizontal scrolling routing in the C.M.I. system software is used.

2.2.9 Sequencer

When recording on the Sequencer (Page 9), a hardware timer located of the Master Card CMI02 is used to measure the elapsed time between events such as key depressions or releases. As each event takes place procesor 1 assembles the keystroke or control change data into a five byte packet along with the time to the next event and queues it. Whe the queue is half full, Processor 2 writes the data to the sequenc file on disk, emptying the queue.

In playback mode, Processor 2 reads the playback file into a queue Processor 1 takes keystroke and timing packets from the queue and set the timer on the Master Card for the time to the next event. When thi time has elapsed, the timer generates an interrupt and the next even is pulled from the queue and played.

The Merge function uses both Record and Playback processe simultaneously.

When running on Internal Synch, the timer operates by counting the system clock. When External Synch is specified, the timer configured to use the external clock, which is derived from the Syn input on the rear of the Mainframe, via suitable signal processi circuitry. The external synch is fed through another programmab timer so that it can be divided if desired.

)

)

C.M.I. MAINFRAME SERVICE MANUAL - Page 8

2.2.10 Music Composition Language

M.C.L. data is store on disk in the form of M.C.L. notation. The Lo command simply causes processor 2 to read the file specified in R.A.M. No processing of the data is done at this stage.

When the Play command is issued, Processor 2 starts compiling t source code and generates keystroke packets which it queues along wi the time to the next event, which it calculates from the combinati of up to eight parts which it may be playing simultaneously. The packets are then processed by processor 1 in much the same way as f the Sequencer (described above).

Internal/External synchronisation works the same way as for t Sequencer.

)

#### 3.0 SPECIFICATIONS

- -,

....+

÷

addition and the state of the s

)

3.1 ELECTRICAL Power Requirements Voltage: 100-120 or 200-250 switch selectable Mains Current: 2 amps @ 240 V, 4 amps @ 120 V Mains Mains Frequency: 50/60 Hz 3.2 AUDIO Channel Cutputs Conrector type: Canron XLR 3 pin (Balanced) Number of Channels: 8 (maximum) Output Level: 3.7 volts p-p Output impedance: 600 ohms Cutput load: Must be greater than 600 ohms Mixed Line Output Same as Channel cutputs Monitor Speaker Output Connector type: Cannon XLR 3 pin Load impedance: 4 ohms (minimum) Power output at clipping: 20 watts max. (This cutput is not intended to be driven to full outp continuously.) Headphone output Connector type: 1/4" Stereo Phones Signal: Derived from monitor speaker output via 100 obm resistor Synch Input Connector type: Cannon XLR 3 pin Level: 1 volt (min) 20 volt (max) p-p. Frequency range: 2 Hz - 5 KHz Impedance: 10XHz Click Cutput Connector Type: Cannon XLR 3 pin approx 5 mS wide, alternative Output signal: 5 volt spike, negative and positive going. Mic Input Connector type: Cannon XLR 3 pin Impedance: 6000 Microphone type: Balanced, high output dynamic or condenser type Line Input Connector type: Cannon XLR 3 pin Input signal: Balanced Sensitivity: 1.4 volts p-p required for full scale conversion. Impedance 600 ohms. ALC Direct Input C.M.I. MAINFRAME SERVICE MANUAL -Page 10

Connector Type: Cannon XLR 3 pin Input Signal: D.C. coupled Sensitivity: 10 volts p-p for full-scale conversion Impedance: 100 K ohms

3.3 DIGITAL

)

)

Processor: Dual M6800

Memory: 64 kilobytes Programme RAM 16 kilobytes Video RAM 128 kilobytes Waveform RAM

Floppy Lisk: 2x YE DATA YD174 8 inch double sided, single density Soft sectored, 128 bytes per sector

Graphics Display: Bit mapped VRAM Composite video output 1 volt p-p nominal 75 ohms impedance

Irput/Cutput: Serial RS232-C, S600 Baud

3.4 MECHANICAL

Dimensions: Width: 750 mm Depth: 450 mm Height: 320 mm

Weight: 40 kilograms

Page 11

#### 4.0 FUNCTIONAL IESCRIPTION

This section describes the operation of each of the circuit boar used in the C.M.I. mainframe. The information is presented primari to give service personel a thorough understanding of the operation the system as an aid to fault diagnosis to the board level. Once t faulty board has been identified, it is recommended that the Mainfra be repaired by board exchange. The faulty item should be returned Fairlight Instruments for repair.

QCC4.1\_9-026\_DUAL\_6800\_CENTRAL\_PROCESSOR\_FUNCTIONAL\_DESCRIPTION

#### 4.1.1 INTRODUCTION

)

)

. .

ŗ,

ź.

The Dual processor card operates each processor into a common addre and data bus in an interleaved manner, each processor therefore m simultaneously access the same memory location without any contenti problems.

This unique manner of operation allows for full "synergistic peration, and either synchronous or asynchronous relationshibetween processors.

The memory addresses are issued to the bus 225 nanoseconds prior the access cycle, allowing addresses to be modified by an extern memory mapping unit card for applications requiring in excess of 6 bytes of memory space. Many global timing signals are issued from t processor, these signals greatly reduce the complexity of many of t other cards in the system.

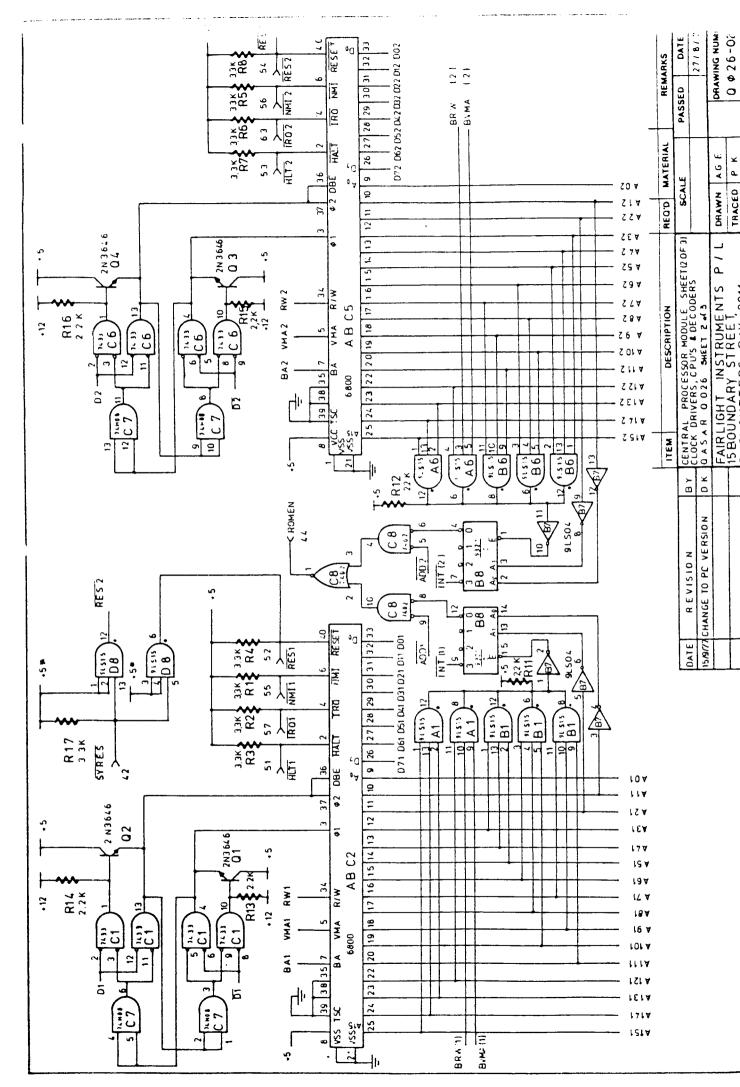

4.1.2 TIMING & MEMORY CONTROL LOGIC (Refer to drawing Q026-01)

4.1.2.1 Master Timing Signals

All system timing signals are derived from crystal-controlled 40% oscillator Q5. Flip-flop E3 divides this pulse train by two to provide a symmetrical 20 MHz square wave, which is made available as a time signal on the bus via E7 on edge connector pin 43. Quad D-type law F2, together with one quarter of quad flip-flop E1, are configured a twisted-tail ring counter which generates 10 unique states each 50 nanoseconds duration. The required states are decoded by NAND gates F3.

4.1.2.2 Dynamic Memory Timing Signals

Four non-inverting buffers of D1 are driven by latch E1 to provide ( (Column Address Strobe), RAS (Row Address Strobe), CA (Column Addre (asserted low) and RA (Row Address, asserted low). RAS is delay relative to CAS by about 20 nS by the propagation delay of A7. RA CA are complimentary signals.

C.M.I. MAINFRAME SERVICE MANUAL - Page 12 Scanned by JB EMOND - www.fairlight.free.fr 4.1.2.3 Data and Address Buss Multiplexing

Flip-flops F4 and F5, along with associated gating, generate th processor drive signals D1, D1, D2 D2 from which the phase 1 and phas 2 clocks for each processor are derived (see next section). The syste address bus is multiplexed by the ADDRESS signals ADD(1) and ADD(2) One-of-four decoders F8 and F9 are used to enable the approprit address and data buffers to the bus to perform the multiplexing. Th data buffer enable signals WRITE1, WRITE2, READ1, READ2 are generate by logical combinations of Phase 2, VMA and Read/Write, performed b F8. The address buss is actually multiplexed four ways, as th vectored interrupt system may also acquire the buss for eithe processor's cycle. The address buffer enables are a function of th Address signal and the Interrupt acknowledge, performed by F4.

Phase 2 reference and Address references for each Processor are fed t the bus via bus drivers.

4.1.2.4 Interrupt Strobe Generation

Fual I-type flip-flop A8 and 3-input ANE gate A7 feed Interrupt Late Strobe pulses to the buss. These are used by the Priority Interrup Control Units (PICUs) used to provide Vectored Interrupts, and also strobe the vector address latches I6 and E( on sheet 3. The PICUs as located elsewhere in the system. These signals strobe the priori latches continuously, until and interrupt is acknowledged. In this wa the Interrupt Priority is maintained at its latest level regardless of delay between an interrupt request being received by the PICU and the associated vector-fetch cycle being executed.

#### 4.1.2.5 Direct Memory Access

ر بو در به

الرقاري والمستحمد والمرور والمستعرف والمستعرف والمستحم والمحادث والمحادث والمحادث والمحال والمحالي والمحالي والمحالي والمحالية و

the of states contained and the

4.

)

DMA requests for each processor are clocked into flip-flop D6 on the falling edge of phase two signals of the respective processors. De acknowledgement is sent to the buss via buffers and the drive signate to the processors are suspended in the phase 1 state for the duration of the DMA cycle. The maximum permissable DMA duration is microseconds. Worst-case DMA latency is 1 microsecond.

4.1.3 CLOCK DRIVERS, CPUs and VECTOR-FETCH DECODERS (Refer to drawing Q026-02)

4.1.3.1 Processor Clocks

Non-overlapping clocks for processor Phase 1 and Phase 2 signals a generated from drive signals D1 and D2. Emitter followers Q1-Q4 a provided to ensure legitimate MOS logic levels as required by the 68 (<.5 volts low, > 4.5 volts high). Cross-coupling between phase 1 a phase 2 drivers ensures that each phase stays low until after to other phase has gone low.

## 4.1.3.2 Vector-Fetch Decoders

A series of open-collector AND gates follow the processor address bu state to detect addresses in the range FFF8-FFFF. The correspond the processor fetching vectors for IRQ, SWI, NMI and RESTART.

Restart vectors come from ROM so when this is sensed the ROM must be enabled and the RAM disabled. This is achieved by the ROMEN (RO ENABLE) signal or Buss pin 44. On detection of an FFFE-FFFF addres (restart being fetched), the one-of-four decoder B8 generates a appropriate signal, and both processors ROMEN is multiplexed onto the bus by OR gate C8.

On detection of and Interrupt Request vector address from th processor, an INT signal is generated by one-of-four decoder B8, whic causes the normal address buss drivers for bits 1 to 4 to be disable and the Interrupt Address buffers (on shhet 3) to be enabled in lieu.

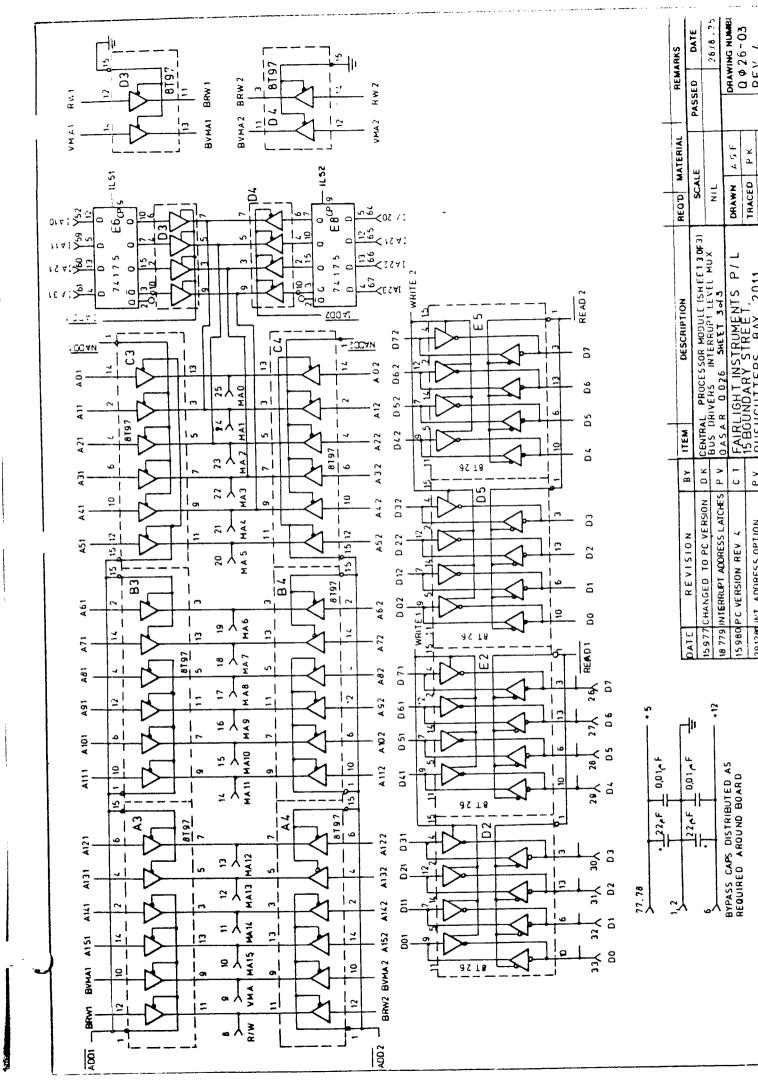

4.1.4 EUSS DRIVERS & INTERUPT LEVEL MULTIPLEXER (Refer to drawing Q026-3)

4.1.4.1 Address Buffers/Multiplexers

Two sets of tri-state buffers are alternately enabled to provid address buss multiplexing. ALD1 and ALD2 enableprocessor 1 an processor two addresses to the buss alternately, except during a DM cycle, in which case the buss is tri-state. Bits 1 to 4 of the address buss are multiplexed between normal processor addresses and addresse coming from the Interrupt Prioritizer, depending on the signals NAD and IADI. When an IPQ vector fetch is attempted, the buffers D3 and D are enabled instead cf the normal address buffers, so that th interrupt priority which has been latched by flip-flops E6 or H become Bits 1 to 4 of the address from which the vector will b fetched. The vector fetch is a double-byte, so address bit Ø is lef un-multiplexed.

4.1.4.2 Lata Buffers/Multiplexers

ing digenter da constituenten 18. etc. e. 1. de - ere - Erender da erender - Erender de Erender - Erender - Erender - Erender - Erender - Erender - Erende Inverting tri-state buffers D2, E2, D5, E5 are used to multiple Processor 1 and Processor 2 data. Data is received when READ is lo and transmitted when WRITE is high.

4.2 <u>CØ32 C.P.U. CONTROL CARE FUNCTIONAL DESCRIPTION</u>

4.2.1 INTROFUCTION

The CPU Control Card provides several support functions required the CPU card. These include startup and bootstrap ROM, seri communications, interrupt prioritisation and a parallel port.

4.2.1.1 Addressing Map

This card occupies the last 4K bytes of the 65K byte phsyical memo addressing space and is set up as follows:-

| FUNCTION                               |

|----------------------------------------|

| Corron ROM                             |

| Common RCM                             |

| 2 unique ROMs, one for each processor  |

| Available for user peripherals         |

| Serial I/O control                     |

| ACIA registers                         |

| PIA registers                          |

| CPU#1 interrupt prioritiser            |

| CPU#2 interrupt prioritiser            |

| Shared 512 byte RAM                    |

| Unique 256 byte RAM for each processor |

|                                        |

4.2.1.2 Restart and Interrupt Vectors

RAM space allocated uniquely to each processor provide independe restart and interrupt vectoring. The vector locations are as follow

| ADDRESS   | VECTCR                                 | VECTCR                                |

|-----------|----------------------------------------|---------------------------------------|

| (HEX)     | (6800 SISTEM)                          | (6809 SYSTEM)                         |

| FFFE/F    | Restart                                | Restart                               |

| FFFC/D    | NMI                                    | NMI                                   |

| FFFA/B    | SWI                                    | SWI1                                  |

| FFF8/9    | Unused                                 | Unused                                |

| FFF6/7    | Unused                                 | FIRQ                                  |

| FFF4/5    | Unused                                 | SWI2                                  |

| FFF2/3    | Unused                                 | SWIC                                  |

| FFFØ/1    | Unused                                 | Unused                                |

| FFEE/F    | IRQ level 7 (lowest)                   | IRÇ level 7                           |

| FFEC/D    | IRQ level 6                            | IRQ level 6                           |

| FFEA/B    | IRQ level 5                            | IRQ level 5                           |

| FFE8/S    | IRQ level 4                            | IRQ level 4                           |

| FFE6/7    | IRQ level 3                            | IRQ level 3                           |

| FFE4/5    | IRQ level 2                            | IRQ level 2                           |

| FFE2/3    | IRQ level 1                            | IRQ level 1                           |

| FFEØ/1    | IRQ level Ø (highest)                  | IRQ level Ø (highest)                 |

| FFDE/F    | Monitor workspace                      | IRQ level 15 (lowest)                 |

| FFDC/D    | Monitor workspace                      | IRQ level 14                          |

| FFDA/B    | Monitor workspace                      | IRQ level 13                          |

| FFD8/9    | Monitor workspace                      | IRQ level 12                          |

| FFD6/7    | Monitor workspace                      | IRQ level 11                          |

| FFD4/5    | Monitor workspace                      | IRQ level 10                          |

| FFD2/3    | Monitor workspace                      | IRQ level 9                           |

| FFLØ/1    | Monitor workspace                      | IRQ level 8                           |

| · - · · - | ······································ | · · · · · · · · · · · · · · · · · · · |

C.M.I. MAINFRAME SERVICE MANUAL - Page 15

4.16 Line In

Balanced, 600 ohm line level input. This input is connected to the Analogue to Digital converter when the MIC/LINE switch is in the LINE position.

Connector Type: Cannon 3-pin

- Pin 1 GROUND

- Pin 2 INPUT A. Amplitude of 1.4 volts P-P required for full scale conversion.

- Pin 3 INPUT B. Amplitude of 1.4 volts P-P required for full scale conversion.

## 4.17 ADC DIRECT

3

)

Direct input to the Analogue to Digital converter when the ADC DIRECT/ MIC LINE switch is in the ADC DIRECT position. Because this input is Direct Coupled, any D.C. offset on this input will result in a D.C. shift of a sound sample.

Connector Type: Cannon 3-pin.

- Pin 1 GROUND

- Pin 2 GROUND

- Pin 3 INPUT. Amplitude for full scale conversion is 10 volts P-P.

4.2.1.4 System Bootstrap/ Disk Controller Firmware

This EFROM is used by Processor 2 for disk operations and occupies locations F800 to FBFF in the unique ROM space for CPU#2. The following functions are provided:-

Boot load operating system from disc Initialise disc controller ≭ × Read full last sector Read partial last sector \* Read verify (CRC check only) \* \* Write and verify CRC \* Restore head (seek track Ø) ≭ Seek to specified track \* Write test Write D.D. mark to sector \* Write sectors and verify CRC \* \* Write sectors and don't verify CRC Check and abort if non recoverable error \*

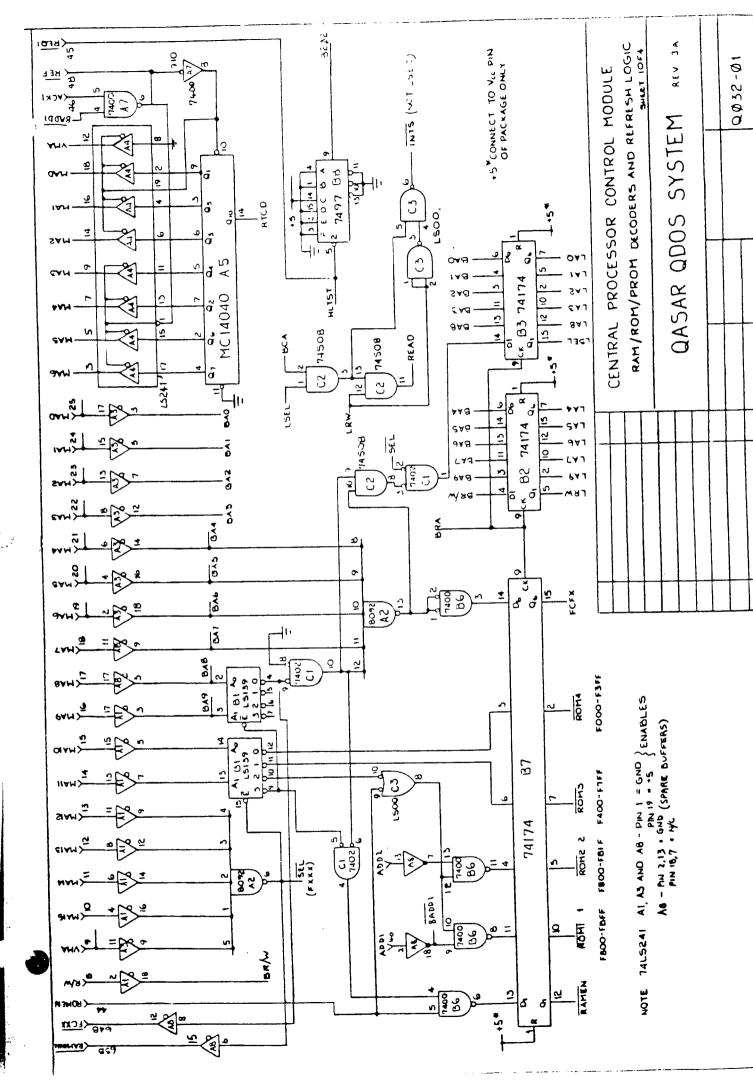

4.2.2 AIDRESS FECODING AND RAM REFRESE CONTROL (Pefer to drawing Q032-01)

4.2.2.1 Address Decoding

**`**\*\*

قرر.

The System Data Buss is buffered by non-inverting buffers A1 and A NAND gate A2 generates an output (asserted LOW) when an address in th range FXXX is detected. This is fed out to the buss on edge connecto pin 65B (RAMINH) to disable RAM when accesses to this address rang are made. Further decoding by one-of-four selectors B1 generate selec signals for the four EPROMS, ROM1 through ROM4. ROM1 and ROM2 are the processor-unique ROMs, which are selected by the ADD1 and ADD (address) signals from the buss, which are gated in by NANE gates B6.

Selection of the on-card static RAM and peripheral devices in the FCFX range are also decoded.

These six select signals are latched by hex flip-flop B7. Hex flipflops B2 and B3 latch the 10 low-order address bits, as well as the READ/WRITE and Card Select signals.

4.2.2.2 RAM Refresh Control

Rate multiplier B8 is configured to produce a 1 microsecond pulse every 16 microseconds. This output (HLTST) generates a DMA request for Processor 1 (REQ1). When this request is acknowledged, by the ACK1 buss signal (asserted HIGH), NAND gate A7 generates a REF (Refresh, asserted LOW) signal on the buss, which signals a refresh cycle to the dynamic RAMs in the system. At the same time, the output of the refresh address counter A5 is driven onto the buss by tri-state buffers A4. At the completion of the refresh (DMA) cycle, the refresh address counter is incremented ready for the next cycle.

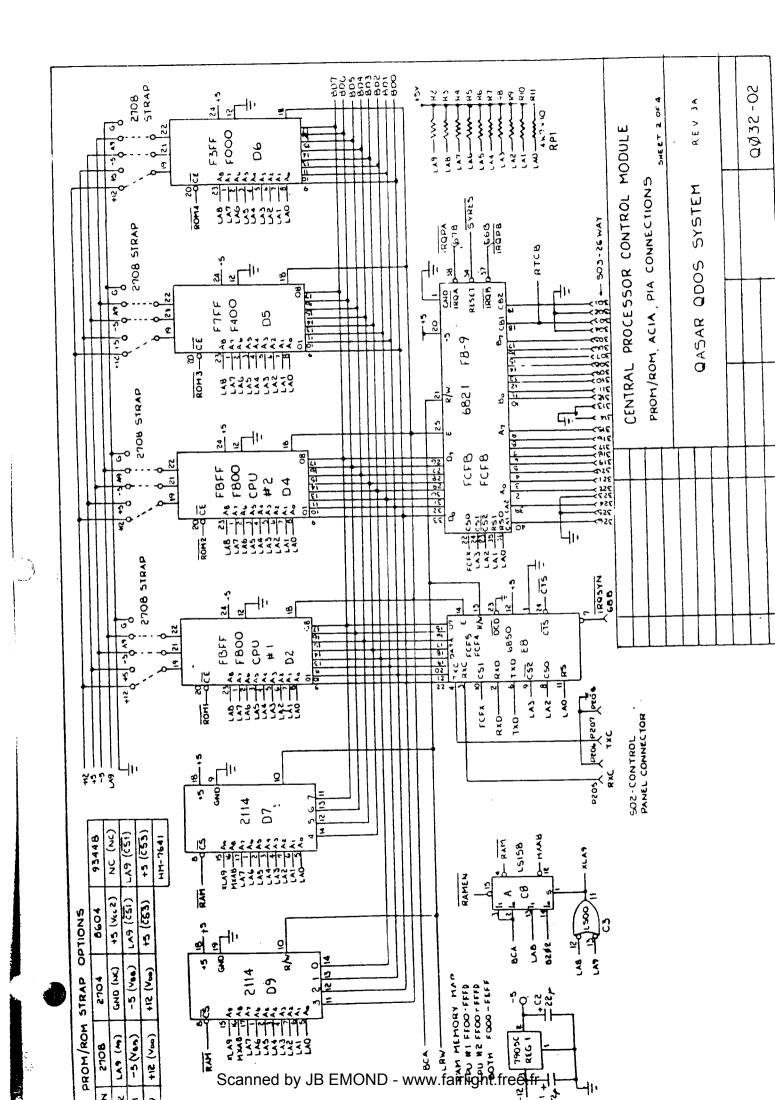

4.2.3 EPROM, RAM, ACIA, PIA (Pefer to drawing Q032-02)

4.2.3.1 Static RAM

A small amount of static RAM is provided for use as scratchpad durin disk calls and monitor firmware execution. It is crganised as follows

CPU #1 FFCO-FFFD CPU #2 FFOO-FFFD Foth FDOO-FFFF

The addressing function for this purpose is generated by multiplexe C8 which is driven by an CR funtion of address bits 8 and 9. The RA itself is in the form of two 1k X 4 devices.

4.2.3.2 FPROM

)

)

4

Four kilobytes of U.V. erasable ROM are used. These are 2708 type.

Their functions are:

| Location | Address Ran <sub>e</sub> e | CPU # | Function                 |

|----------|----------------------------|-------|--------------------------|

| Ľ2       | F800-FBFF                  | 1     | Startup and clock        |

| E 4      | F800-FBFF                  | 2     | Disk boot and controller |

| I5       | F400-F7FF                  | Both  | I/O functions            |

| Dε       | F000-F3FF                  | Both  | Debug monitor            |

4.2.3.3 ACIA (Asynchronous Communications Interface Adapter)

A 6850 ACIA (F8) is used to receive and transmit serial data. The BAU rate is determined by seperate Receive and Transmit Clock siganls coming from the baud-rate generator on the front panel card (0036) vi the 26-way ribbon catle on the front edge of the 0032 card.

Interrupts generated by the ACIA go to the system buss via pin 68B o the edge connector.

Data input and cutput level conversion for the RS232 standard i provided by circuitry on Sheet 3.

4.2.3.4 PIA (Peripheral Interface Adapter)

A PIA (F8,9) is used to provide two general purpose parallel ports Peripheral connections are made through a 26-way ribbon cabl connector on the front of the card.

Interrupts from the PIA are presented to the bus via pins 66B and 67B

The PIA is also used by processor 1 to provide a real-time cloc function via its CB1 input which is clocked continuously by RTC pulses coming from the refresh address counter A5 on sheet 1.

4.2.4 TERMINAL INTERFACE, MANUAL CONTROLS, POWER-ON RESET

4.2.4.1 Terminal Interface

)

and an an and a second and a

RS232 receivers and drivers are provided to interface the ACIA to serial data to and from peripheral devices. F1 is the RS232 driver Two data output paths are provided, called DATAØ and DATA1. Device control signals DONØ and DON1 are used to enable external peripherals The serial-I/O control latch D1 is used to select which of the data paths is enabled, and which devices are switched on. It is configured by writing to FCFØ. As well as selecting data cutput paths, bits 2 and 3 of this latch select which of two busy flags are enabled to the CTS pin of the ACIA.

Bit 4 of the Serial I/O control is used to select the polarity of the busy flag by maens of exclusive-or gate E1.

Bit 5 is used to control the threshold of the busy flag bits of RS23 receiver F2. When bit 5 is HIGH, transistor 01 is held off, and regative bias is applied. With bit 5 LCW, C1 turns on and biases th receivers positively.

The opto-isolator is not normally used, but its outputs are availabl at the edge connector if required. It is turned on by writing Ø1 t the two high bits of the serial I/C control latch.

4.2.4.2. Manual Controls

Restart and interrupt contols are provided on the front-panel car Q036. The push-button switches are debounced by R/S flip-flops made u by gates in F3. Processor selection is aceived by NAND gates F6, whic also drive the buss.

Processor Halt controls are latched by flip-flops F5. This debounce the switches and also ensures that the 6800 timing requirements fo HALT control are met.

When a WAIT state has been achieved, the Buss Available signals fro the CPU card W1 and W2 drive open-collector buffers E5 to turn on th WAIT LELS on the front panel.

4.2.4.3 Power-on Reset

555 Timer E3 is used to generate a system reset signal on power-up This is a low-going pulse of about 500 milliseconds on buss pin 42.

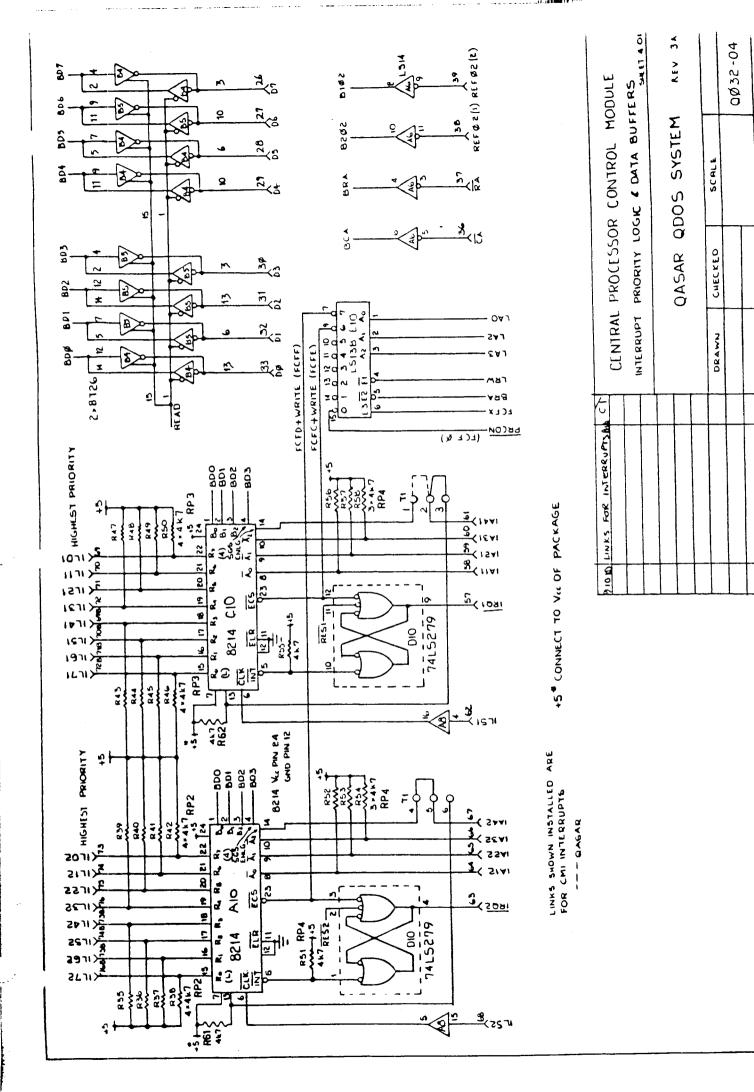

4.2.5 INTERRUPT PRIORITY LOGIC AND DATA EUFFERS (Refer to drawing Q032-04)

4.2.5.1 Interrupt Priority Logic

8214 Priority Interrupt Control Units (PICU) are used to late interrupt requests and generate a priority level which is used by th CPU card to create an interrupt vector address.

The priority level for each PICU is established by writing the compliment of the desired priority level into the status rtegister. The address for CPU 1 is FCFD, for CPU 2 it is FCFC. Decoding for this purpose is performed by one-of-eight selector E10.

Interrupt requests generated by the PICU are latched by flip-flop D10, which are reset when the PICUs are written to to establish th new priority level mask.

The PICUs are clocked by Interrupt Latch Strobe signals from the bu (ILS1 and ILS2).

Each PICU supports up to eight levels of interrupt. To expand t beyond eight, the FICUs can be daisy-chained by changing links o terminal strip T1.

4.2.5.2 Data Buffers

Inverting tri-state buffers B4 and B5 interface the local data buss t the system data buss. The direction of data transfer is controlled b PEAD.

1

-12-22

۰.

)

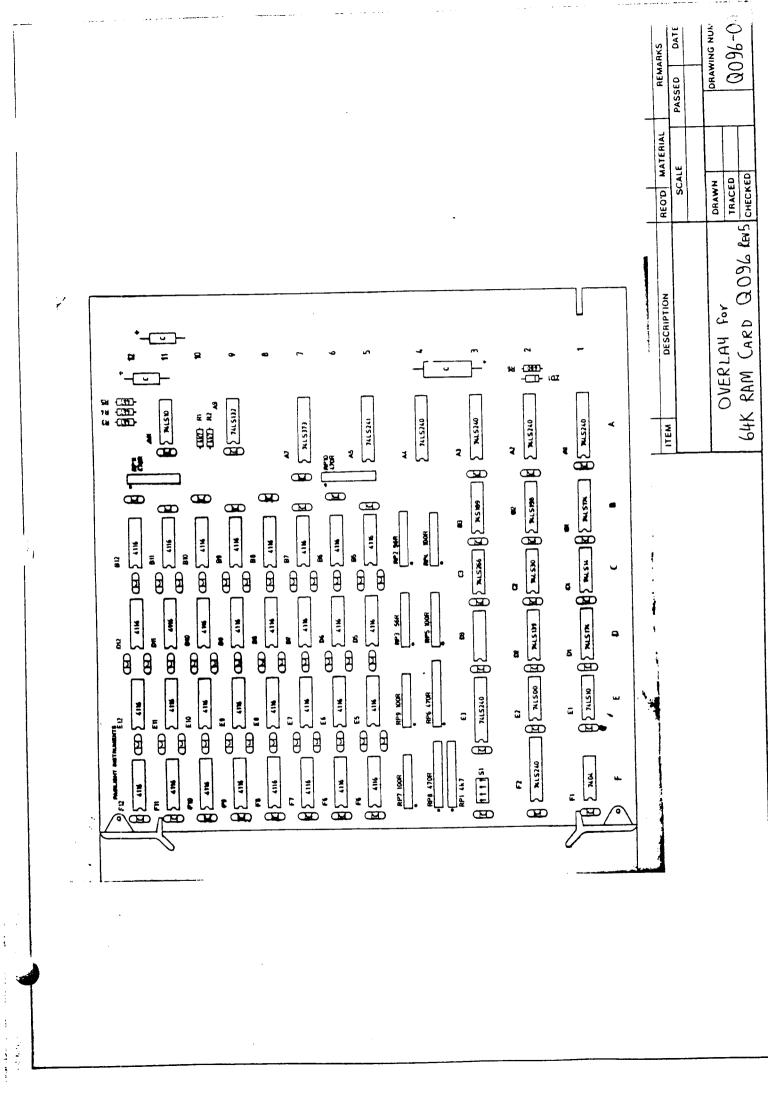

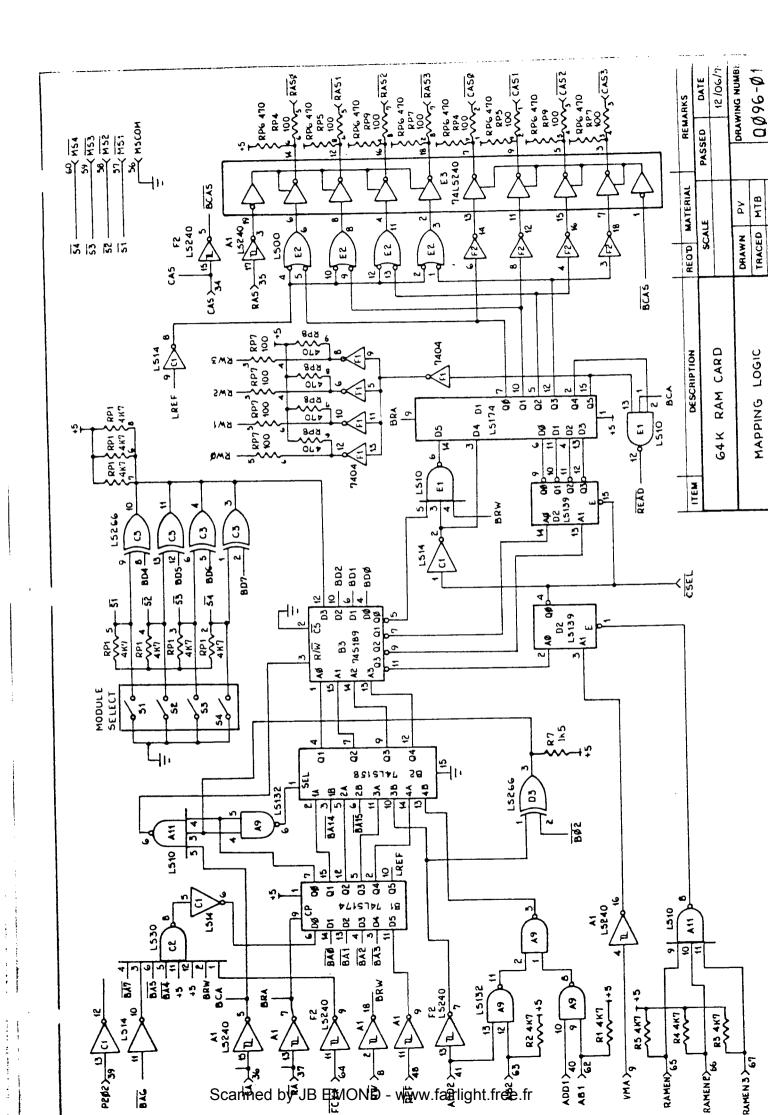

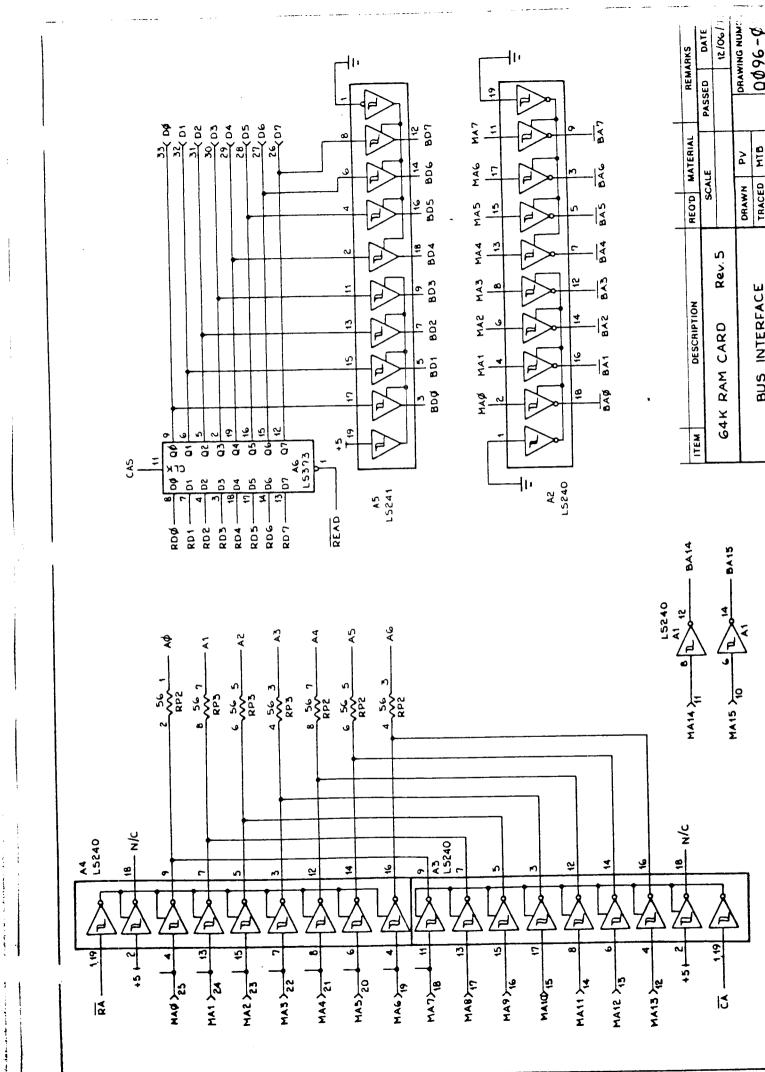

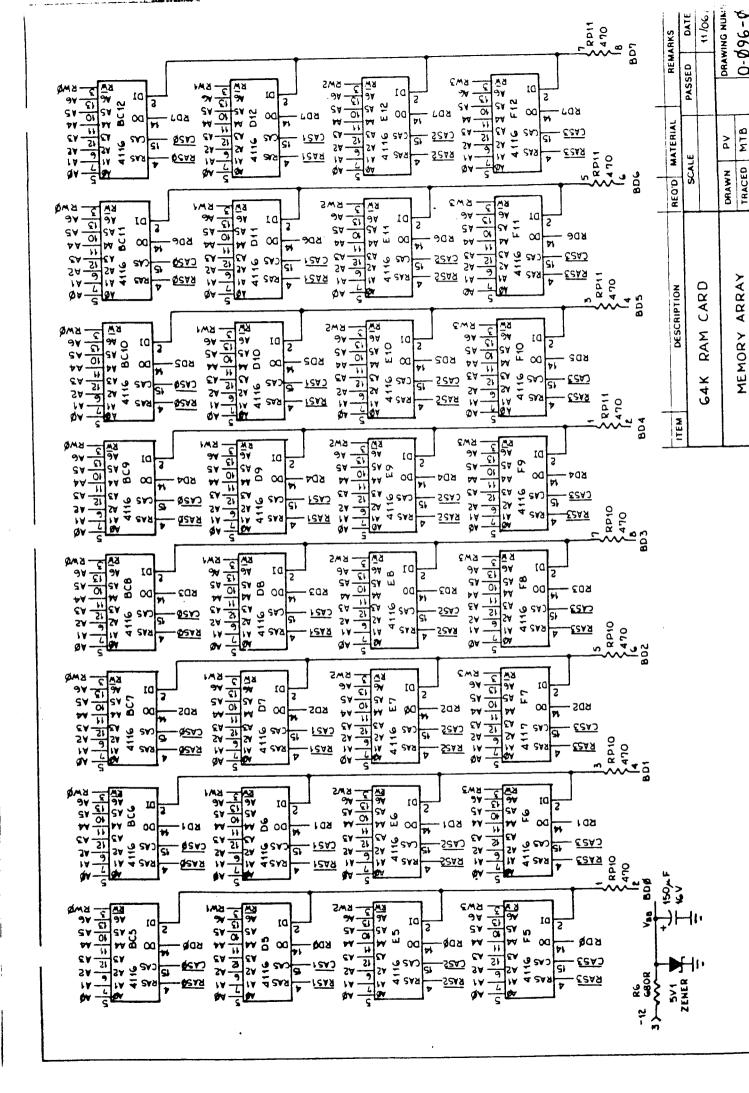

## <u>CCQ4.3\_C-096\_64K\_MAPPING\_RAM\_CARD\_FUNCTIONAL\_DESCRIPTION</u>

#### 4.3.1 INTRODUCTION

The 64K RAM Card contains  $32 \times 16K \times 1$  bit dynamic RAM chips. The RAM runs at a cycle time of 500 nS and is refreshed by a global refresh system contained on the Processor Control Card.

In addition to the dynamic RAM, a fast 16 x 4 bit static RAM is used to provide an independent mapping of each of four 16K logical processor spaces to the 64K physical address space. This mapping RAM is also responsible for enabling the entire card when more than one 64K RAM card is installed in the system. A four-bit module select switch is used for this purpose.

4.3.2 AIDRESS DECODING & MAPPING LOGIC (Refer to drawing Q096-01)

#### 4.3.2.1 Address Decoding

The mapping register base occupies memory space from FC40 to FC4F. Accesses to these addresses are decoded by NAND gate C2, and latched by D-type flip-flop B1. The low four bits of the address are also latched by B1 and these are selected by 4-bit multiplexer B2 when writing to FC4X.

#### 4.3.2.2 Mapping Logic

· ... i...

ł

ł

The mapping register B3 is a high-speed RAM of 16 words of 4 bits. When writing to the mapping register, the four high data bits are compared to the module number set up on the Module Select D.I.L. switch, and if it matches, a 1 is written to data bit 3. This bit is used as the card enable bit when subsequent accesses are made to the RAM. Bit zero is a 0 for write protect, bits 1 and 2 select which of the four 16k blocks is enabled.

When accesses are made to the main RAM, the high two bits of the address along with the address1/address2 multiplex signal and the mapA/mapB select signal form the address to the mapping register. Late bits 0 and 1 from the mapping register select one-of-four blocks via selector I2, which is enabled by a logic zero on bit 3. The block select bits, card select and Read/Write are latched by flip-flop D1.

The card select, read/write and Column Address (BCA) are ANDed by E: to produce the READ enable for the data buffers (on sheet 2). The read/write signal is buffered by inverters F1 and drive the read/write busses for the RAM array via series termination resistors.

The four block select signals are used to gate the Column Address Strobes (CAS) and Row Address Strobes (RAS) which drive the RAM array via buffer H3. Luring Refresh cycles, all four RAS signals are enabled by gates E2, enabled by the latched refresh signal (LREF) from flipflop B1.

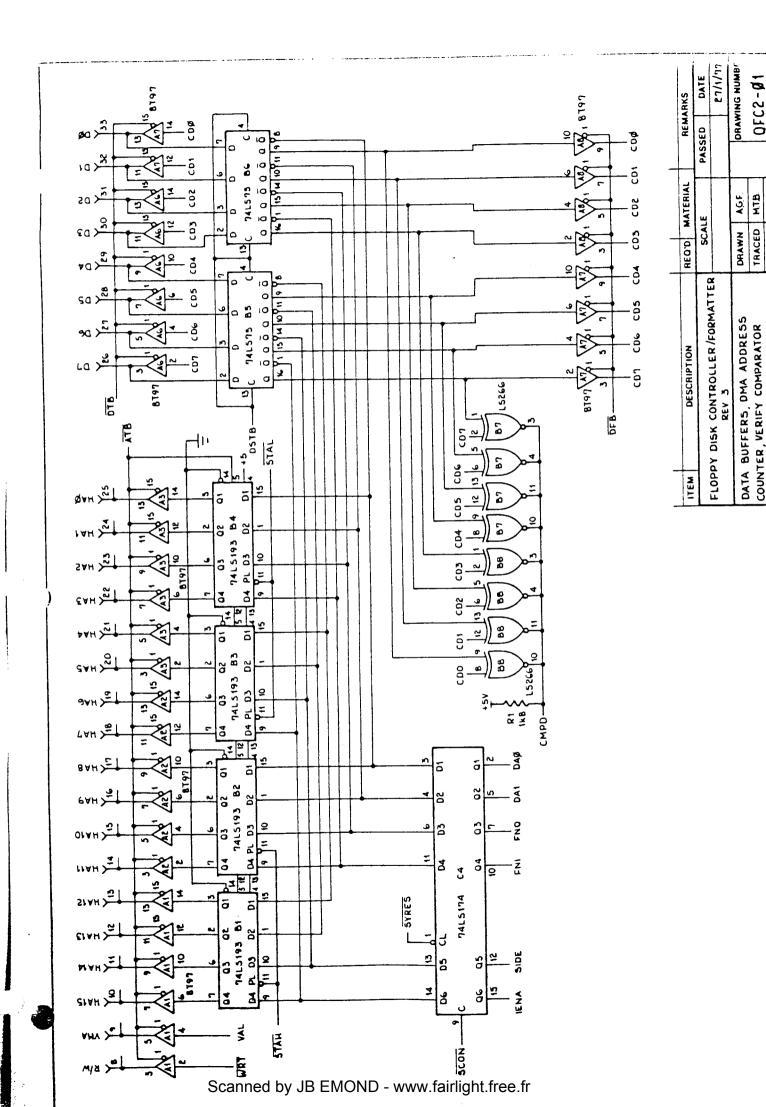

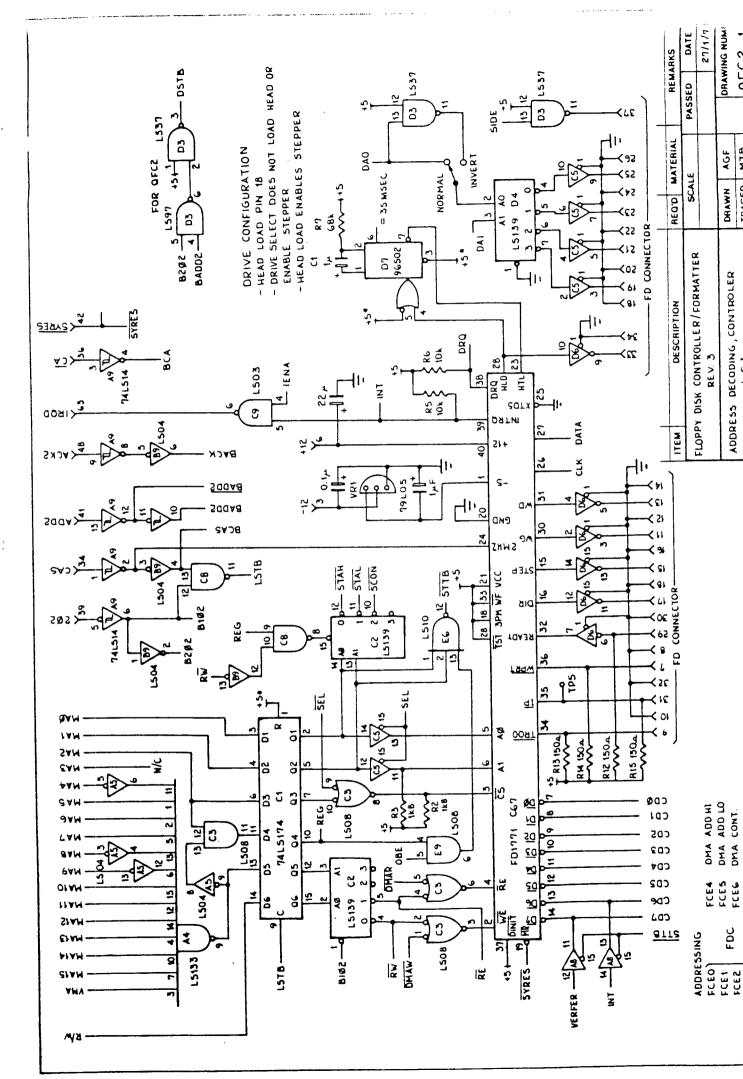

# 4.4 <u>QFC2\_FLOPPY\_DISK\_CONTROLLER\_FUNCTIONAL\_DESCRIPTION</u>

## 4.4.1 INTROLUCTION

The Floppy Disc Controller/Formatter uses a Western Digital FD1771 controller LSI. It is designed to work with CPU #2, transferring data to and from memory by DMA on Processor 2. Once a data transfer is set up the processor may continue processing other tasks until the interrupt for "command done" is issued by the controller.

4.4.1.1 Address Map

| ADDRESS | (HEX) | REAL        | WRITE              |

|---------|-------|-------------|--------------------|

| FCEØ    | •     | status read | command reg        |

| FCE1    |       | track reg   | track reg          |

| FCE2    |       | sector reg  | sector reg         |

| FCE3    |       | data reg    | data reg           |

| FCE4/5  |       | -           | DMA start address  |

| FCE6    |       |             | DMA mode/drive sel |

| FCE7    |       | IMA status  | -                  |

The DMA transfer byte count is inherent in the transfer type.

4.4.1.2 Commands

٠ŕ

こうしょう あいまたいろうし 御をたけ あたい

The following commands may be issued to the command register to effect disc operations:-

```

Restore head to track zero

*

#

Seek to track

Step in current direction

*

*

Step in

×

Step out

≭

Read (single/multiple)

*

Write (single/multiple)

#

Read address mark

Read track (format information)

*

Write track (format information)

*

*

Force interrupt.

```

Various options exist within commands which specify step rate, head loading, address verification, and other actions desirable during the execution of the command.

For full details of these commands, refer to the FD1771 manufacturers data sheets.

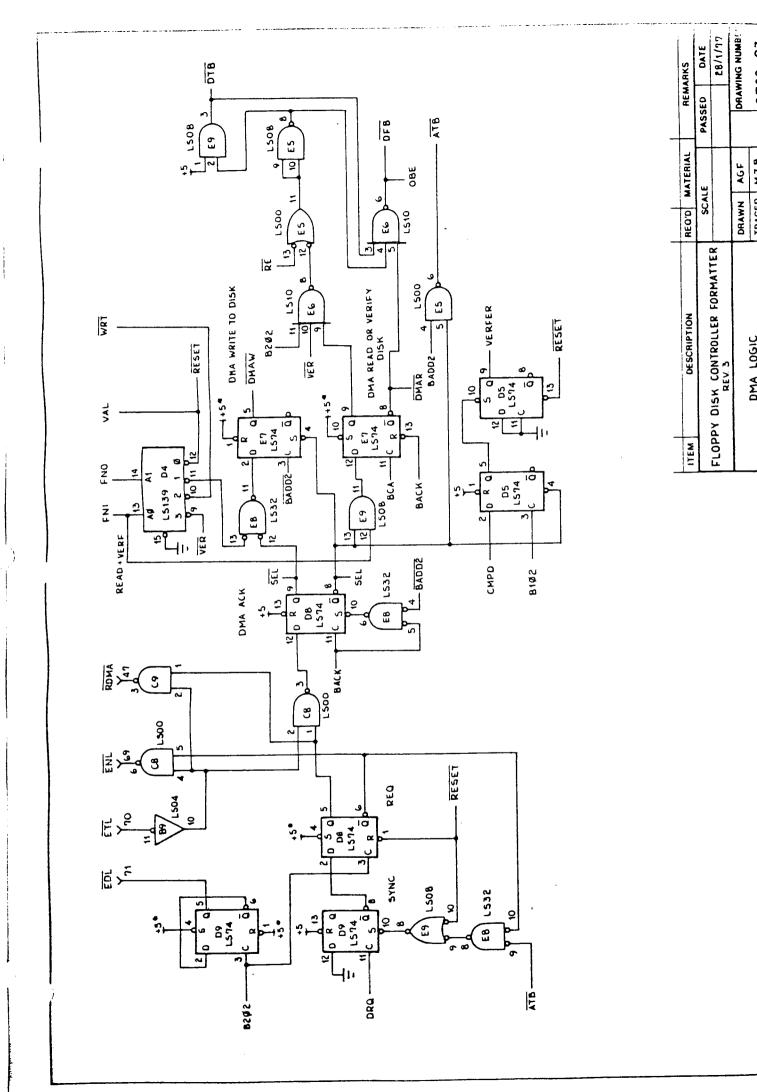

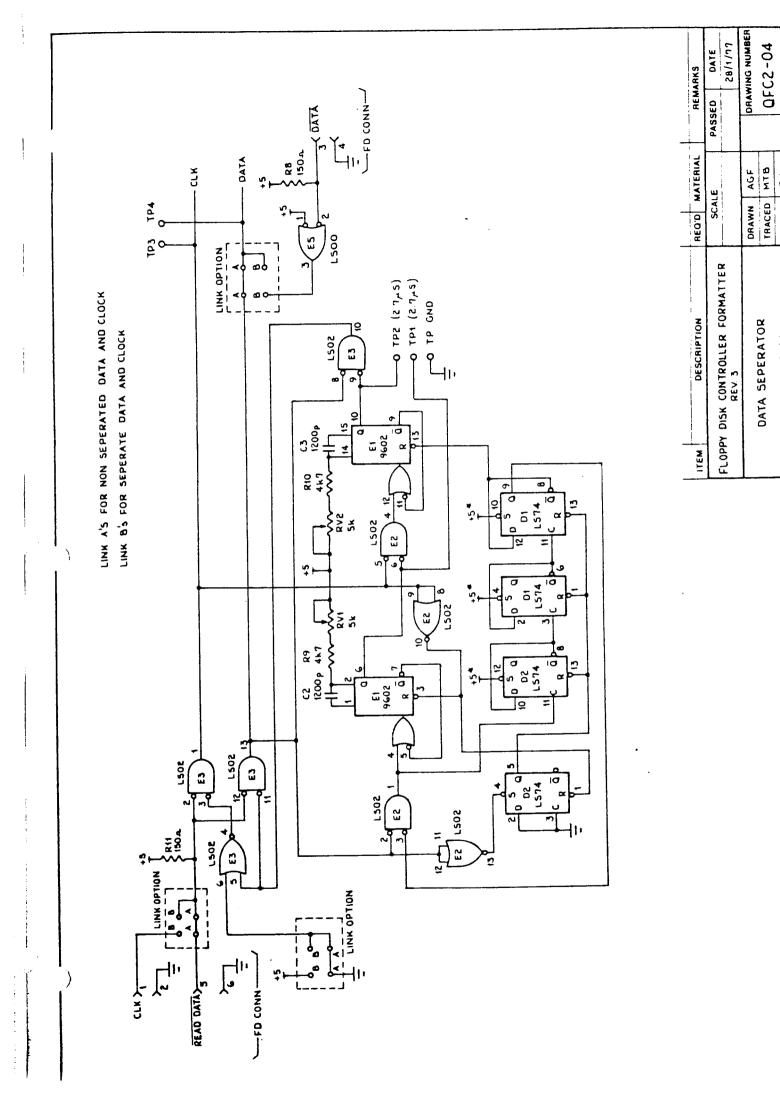

4.4.2 DATA BUFFERS, DMA ADDRESS COUNTER, VERIFY COMPARATOR (Refer to drawing QFC2-01)

4.4.2.1 DMA Address Counters

Sixteen bit counter chain B1 to B4 is used to provide the address for DMA transfers. The starting address for each disc transaction is established by writing the double-byte address to location \$FCE4. This causes the address to be preset into the DMA address counter by means of parallel-load strobe pulses STAL (low byte) and STAH (high byte).

4.4.2.2 Lata Buffers

Data is propagated from the system data bus via latches B5 and B6 which hold the data across the processor 1 phase. This latched data also become the DATA FROM BUS via buffers A7, A8 to the floppycontroller L.S.I.

Lata written to the system control byte at \$FCE6 is latched by hex Dtype flip-flop C4. DA0, DA1 are DRIVE SELECT addressing for selecting which of four disk drives is enabled. FN0, FN1 are FUNCTION SELECTS, which choose one of RESET (00), WRITE (01), READ (10), VERIFY (11).

Bit 4 of the system control byte selects which side of the disk is being accessed when used with dual-sided disk drives. Bit 5 is an INTERRUPT INABLE.

4.4.2.3 Verify Comarator

A special feature of the QFC2 is the ability to verify data from disk against memory without actually transferring it.

EXCLUSIVE-OR gates B7,B8 are used to compare D.M.A.derived data to data read from disk from the controller L.S.I. data CD0-7.

4.4.3 AIDRESS IECODING, CONTROLLER L.S.I., DRIVE SELECT (Refer to drawing GEC2-01)

4.4.3.1 Address Decoding

Address range \$FCEX is decoded by gates A4 and C3 and latched by C1. The clock for this latch (LSTB) is a derivative of processor two phase two, which makes the QFC2 processor two unique. The on-card buss operates at 1MHz, half the system speed.

Addresses FCE0-FCE3 are used by the FD1771. Addresses FCE4-FCE7 are used to write to the DMA address counters and funtion select latch These are enabled by the appropriate outputs from one-of-four selecto: C2.

4.4.3.2 Controller L.S.I.

. . . . . .

. .

and the second second

The -5 volt supply required by the FD1771 is derived from the -12 volsupply by a 79L05 voltage regulator I.C.

Inverting buffers D6 are used to interface the FD1771 L.S.I controller to the disc drive cable. Incoming disc status signal TRØØ (track Zero), IP (Index Pulse), WPRT (write protect) and READ are pulled up by 150 ohm terminating resistors.

The Interrupt Request from the L.S.I. (INTRQ) is gated with th Interrupt Enable (IENA) to provide an open-collector interrupt signa for the system I.R.Q.

One-shot D7 is the 35ms head load timer (see FD1771 data sheet). 4.4.3.3 Drive Select

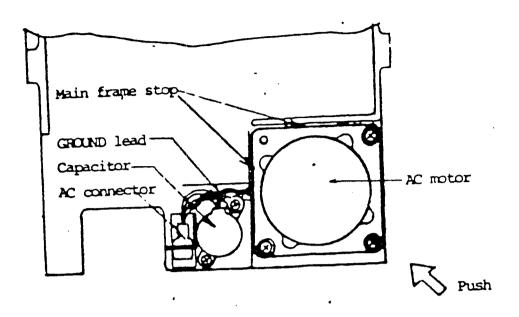

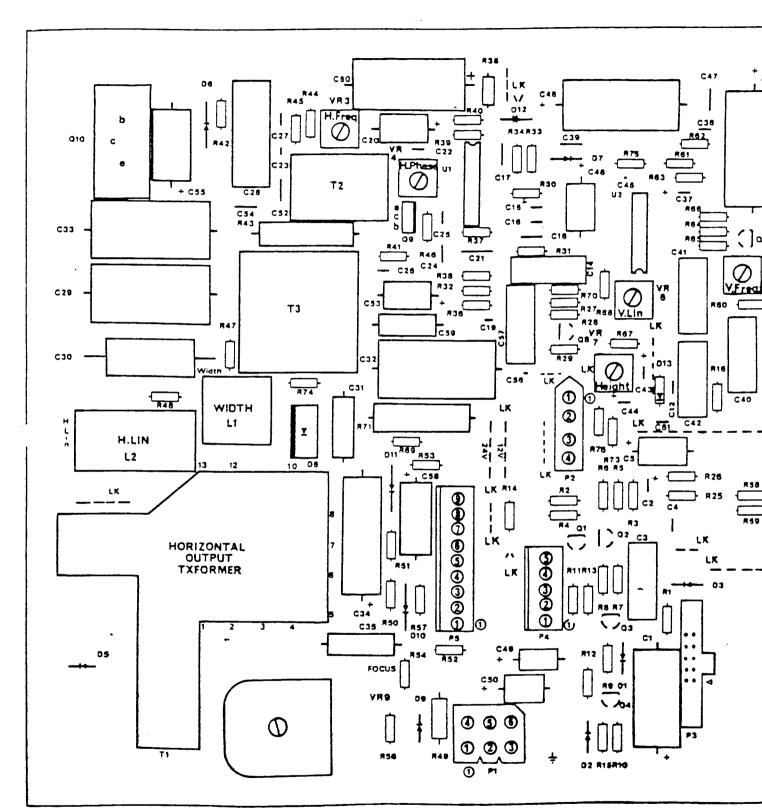

C.M.I. MAINFRAME SERVICE MANUAL - Fage 24